# 620-0048 & 620-0052 Data Collection Modules User Manual

620-8980

Rev. C

06/92

Supersedes: 12/89

## Copyright, Notices, and Trademarks

Printed in U.S.A. – © Copyright 1987 by Honeywell Inc.

Revision C – June 1, 1992

While this information is presented in good faith and believed to be accurate, Honeywell disclaims the implied warranties of merchantability and fitness for a particular purpose and makes no express warranties except as may be stated in its written agreement with and for its customer.

In no event is Honeywell liable to anyone for any indirect, special or consequential damages. The information and specifications in this document are subject to change without notice.

This document was prepared using Information Mapping® methodologies and formatting principles.

Honeywell 620 Logic Controller System® and 620 LCS® are registered trademarks of Honeywell, Inc.

Information Mapping is a trademark of Information Mapping, Inc.

Belden is a registered trademark of Cooper Industries.

Honeywell

Industrial Automation and Control

Automation College

1100 Virginia Drive

Fort Washington, PA 19034

(215) 641-3126

## **About This Publication**

This publication provides comprehensive information, including protocol and instructions, for interfacing the Model 620-0048 or Model 620-0052 Data Collection Module (DCM) with a general purpose computer. Features and functions that differ between the two modules are described separately throughout the manual.

For applications in which a DCM is interfaced with a 627 MiniCOP microcomputer using Honeywell communications software, only the installation, configuration, and theory of operation sections (Sections 2, 3, and 4) of this manual apply. Other user information is contained in the user manual of the host device interfaced by the DCM.

This manual, Revision C, is intended for use with Revision 3.1 620-0048 firmware and Revision 2.0 620-0052 firmware.

# **Table of Contents**

| SECTION 1 -             | DATA COLLECTION MODULES (DCMs) |     |

|-------------------------|--------------------------------|-----|

| Overview                |                                |     |

| DCM Func                | tional Description             | 6   |

|                         |                                |     |

| SECTION 2               | - DCM INSTALLATION             | 9   |

| Overview                |                                |     |

|                         | e DCM Module                   |     |

|                         | stallation                     |     |

| DCM Wirin               | ıg                             | 17  |

| SECTION 3 -             | DCM CONFIGURATION              | 97  |

| Overview                |                                |     |

|                         | DCM DIP Switch Settings        | 27  |

| 620-00 <del>4</del> 8 L | OCM DIP Switch Settings        | ∠0  |

| 020-0032 L              | OWI DIE SWIICH Sellings        | 40  |

| SECTION 4               | DCM THEORY OF OPERATION        | 49  |

| Overview                |                                | 10  |

|                         | ation                          |     |

|                         | Link Control                   |     |

| DCM Excha               | ange Procedures                | 65  |

| Flag Mode               | Operation                      | 72  |

| Data Collec             | tion Mode                      | 73  |

| Session Ex              | kecution Time                  | 76  |

| Error Reco              | very                           | 79  |

| DCM Progra              | am Memory Checksum             | 80  |

| SECTION 5               | DCM INSTRUCTION SET            | 0.0 |

|                         |                                |     |

| Overview                |                                | 83  |

| Input/Outpu             | ut Instructions                | 87  |

| Data Collec             | ction Instructions             | 93  |

| Register ins            | structions                     | 104 |

| 620 LCS PI              | rocessor Control Instructions  | 115 |

| Program M               | lemory Instructions            | 122 |

| Program H               | eader Instructions             | 128 |

| Instruction             | Instructions                   | 135 |

| Flog Mode               | Execution Times                | 139 |

| From Mass               | Operation Responseages         | 145 |

| LITOI WIESS             | oayes                          | 140 |

| APPENDIX                |                                | 159 |

| Overview                |                                | 150 |

|                         | iction Set Opcodes             | 160 |

| ASCII-to-De             | ecimal Conversion              | 165 |

| 7.00m to De             |                                | 103 |

| GLOSSARY                |                                | 167 |

|                         |                                |     |

| INDEX                   |                                | 171 |

| Figure 1-1  | 620-0048 DCM Frontplate 6                                                 |    |

|-------------|---------------------------------------------------------------------------|----|

| Figure 1-2  | 620-0052 DCM Frontplate7                                                  |    |

| Figure 2-1  | Point-to-Point Configuration11                                            |    |

| Figure 2-2  | Multipoint/Multidrop Configuration11                                      |    |

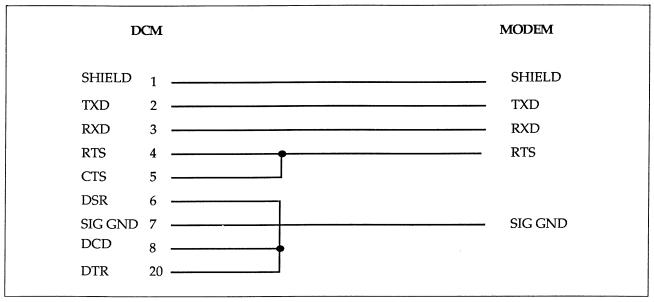

| Figure 2-3  | RS232 Connection to Full Function Modem                                   |    |

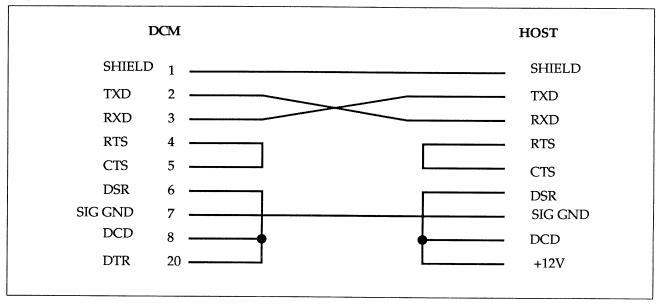

| Figure 2-4  | RS232 Connection to Minimum Function Modem                                |    |

| Figure 2-5  | RS232 Connection to Host23                                                |    |

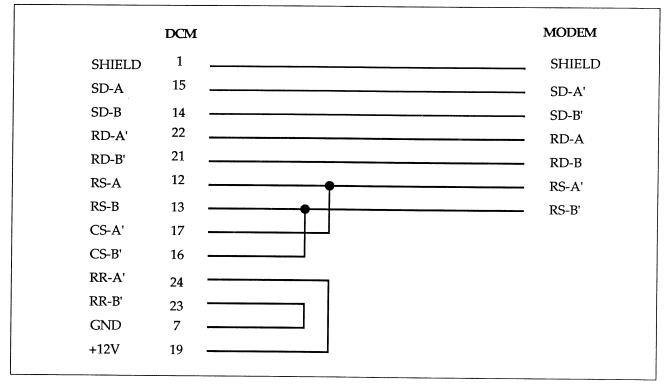

| Figure 2-6  | RS422/RS485 Connection to Minimum Function Modem23                        |    |

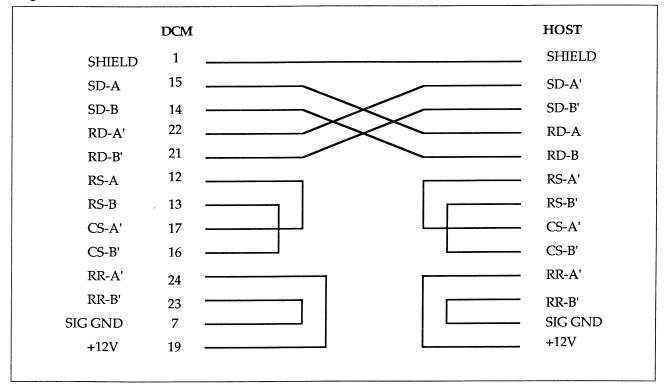

| Figure 2-7  | RS422/RS485 Connection to Host                                            |    |

| Figure 2-8  | RS422/RS485 Single Twisted-Pair Network Connection                        |    |

| Figure 2-9  | RS422/RS485 Two Twisted-Pair Network Connection                           |    |

| Figure 3-1  | 620-0048 DCM DIP Switches                                                 |    |

| Figure 3-1  | DCM Serial Port with Multidrop Control                                    |    |

| Figure 3-2  | DCM Terminating Resistor Locations                                        |    |

|             | 620-0052 DCM DIP Switches                                                 |    |

| Figure 3-4  |                                                                           |    |

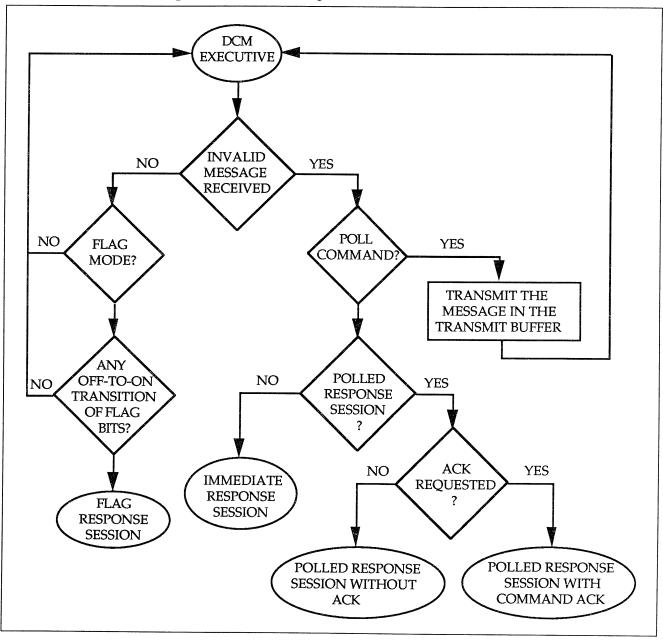

| Figure 4-1  | DCM Response Mode Flow Diagram                                            |    |

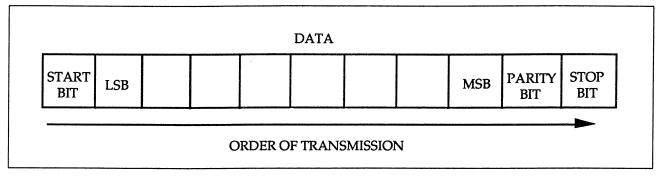

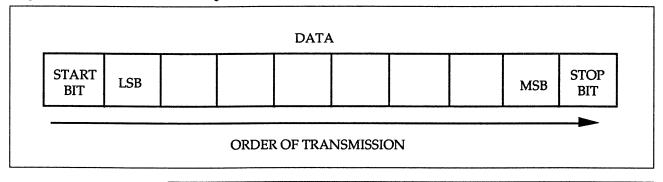

| Figure 4-2  | ABC Protocol Character Format                                             |    |

| Figure 4-3  | ABC Protocol Optional Character Format                                    |    |

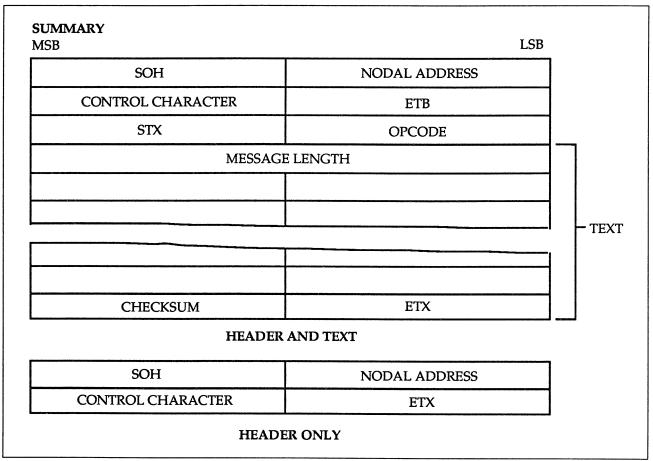

| Figure 4-4  | Header and Text Message Format                                            |    |

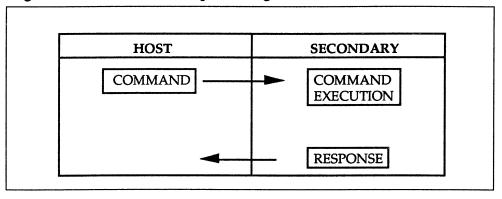

| Figure 4-5  | Immediate Response Diagram66                                              |    |

| Figure 4-6  | Immediate Response Session                                                |    |

| Figure 4-7  | Polled Response Session Without Acknowledge                               |    |

| Figure 4-8  | Polled Response Diagram69                                                 |    |

| Figure 4-9  | Polled Response Session With Acknowledge70                                |    |

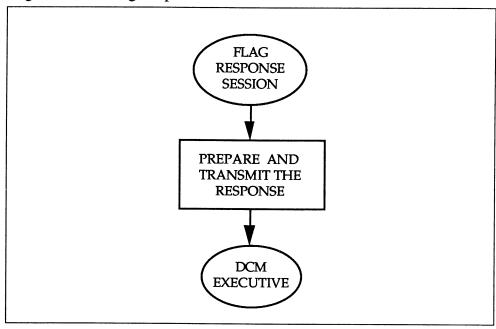

| Figure 4-10 | Flag Response Session71                                                   |    |

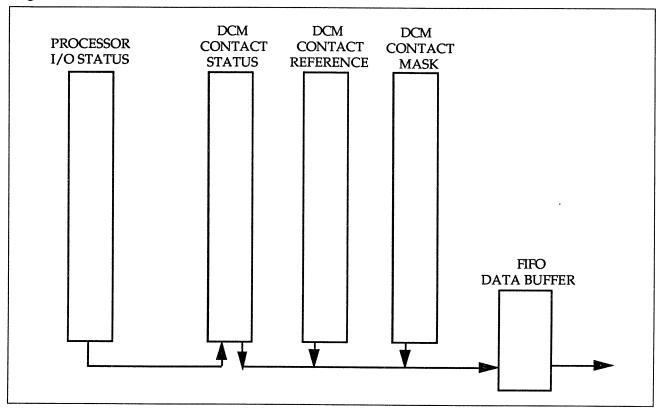

| Figure 4-11 | DCM I/O Status Tables73                                                   |    |

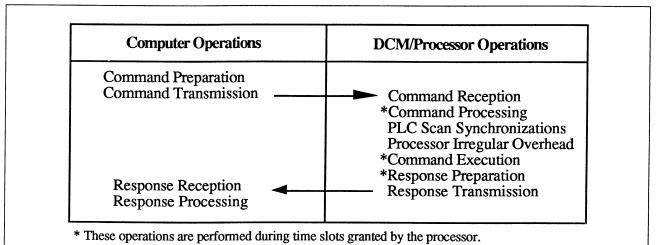

| Figure 4-12 | Operations in Session Execution Time                                      |    |

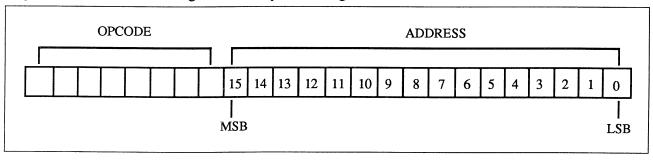

| Figure 4-13 | 620 LCS Program Memory Word Organization80                                |    |

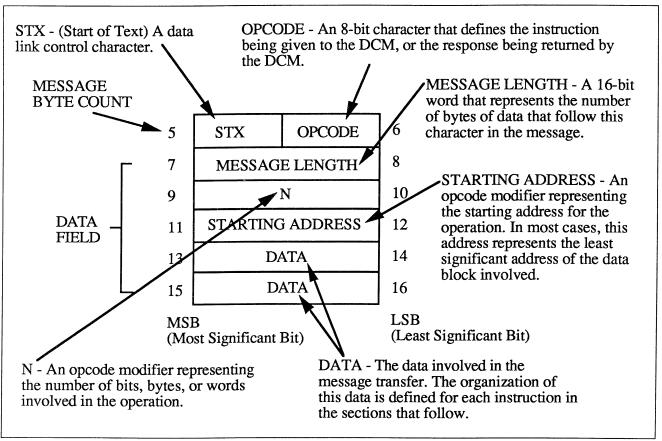

| Figure 5-1  | General Message Text Structure for 620-0048/0052 DCMs84                   |    |

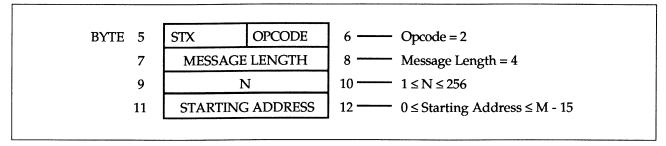

| Figure 5-2  | Read 16N I/O Instruction Format88                                         |    |

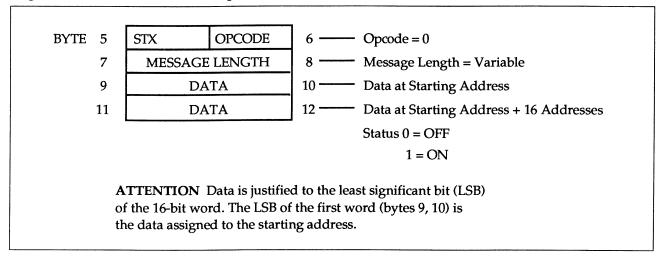

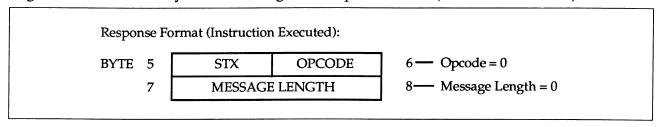

| Figure 5-3  | Read 16N I/O Response Format (Instruction Executed)88                     |    |

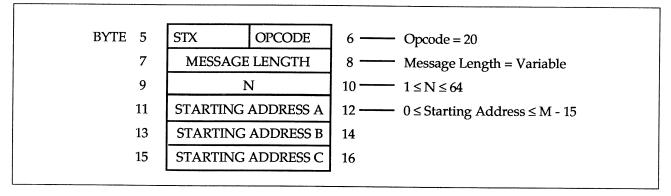

| Figure 5-4  | Read 16N Scattered I/O Instruction Format89                               |    |

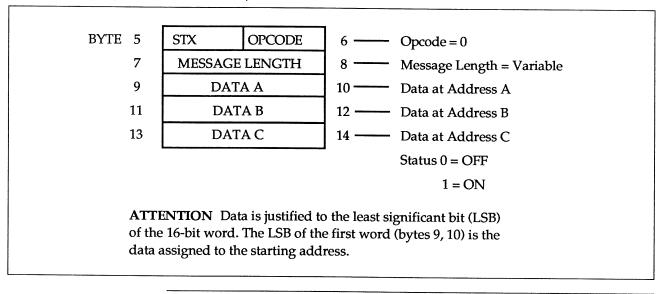

| Figure 5-5  | Read 16N Scattered I/O Response Format (Instruction Executed) 89          |    |

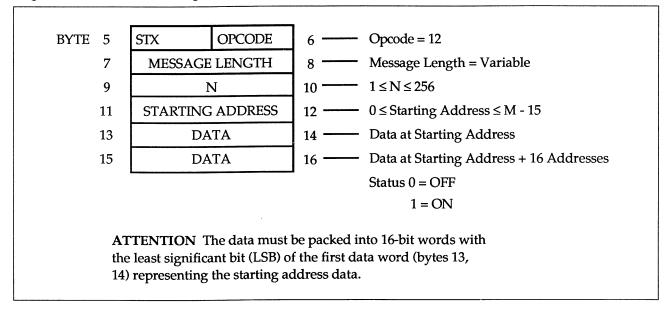

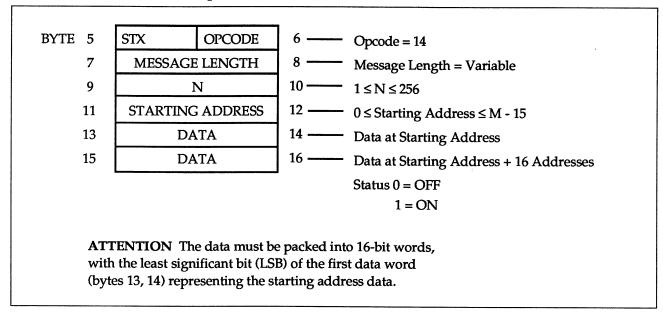

| Figure 5-6  | Write N Outputs Instruction Format90                                      |    |

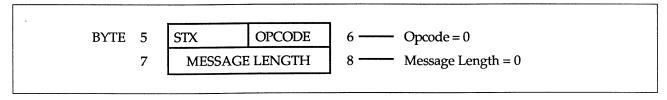

| Figure 5-7  | Write N Outputs Response Format (Instruction Executed)90                  |    |

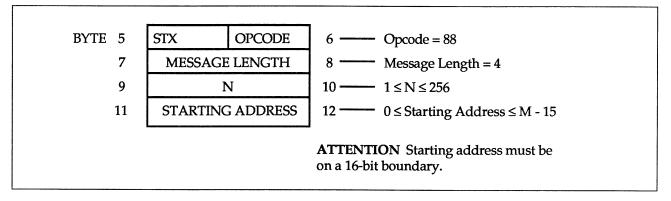

| Figure 5-8  | Write 16N Outputs Instruction Format                                      |    |

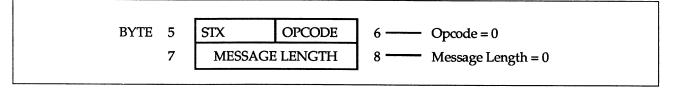

| Figure 5-9  | Write 16N Outputs Response Format (Instruction Executed)                  |    |

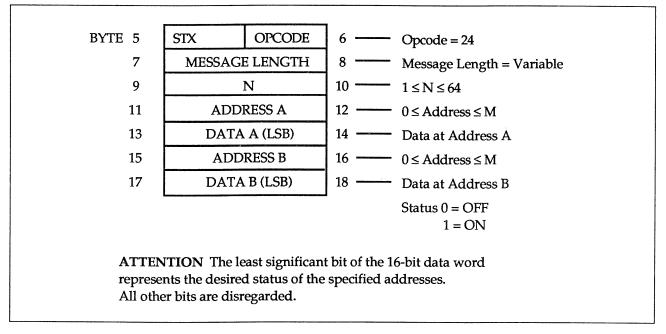

| Figure 5-10 | Write N Scattered Outputs Instruction Format                              |    |

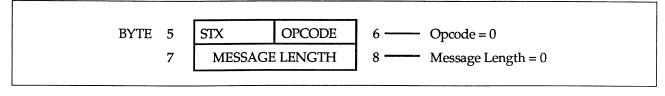

| Figure 5-11 | Write N Scattered Outputs Response Format (Instruction Executed)92        |    |

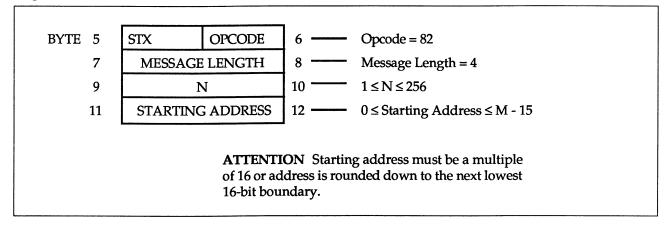

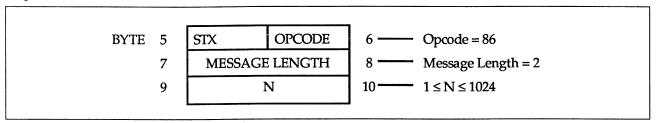

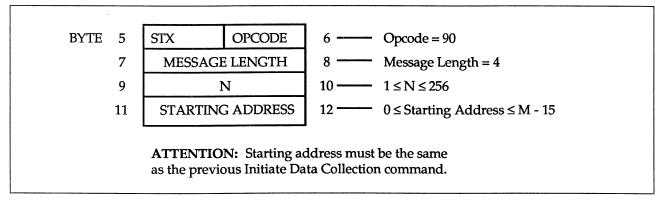

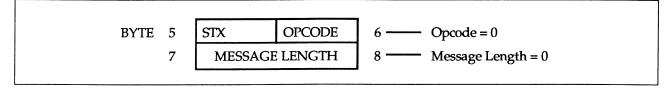

| Figure 5-12 | Initiate Data Collection Instruction Format                               |    |

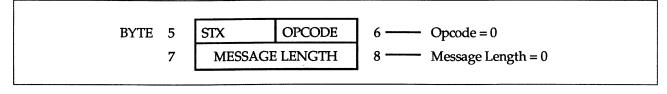

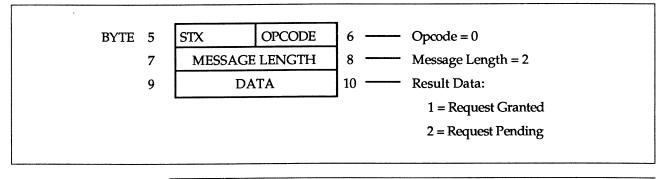

| Figure 5-13 | Initiate Data Collection Response Format (Data Collection in Progress) 94 |    |

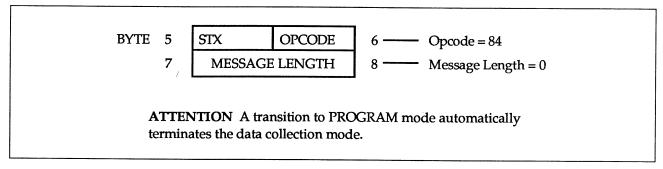

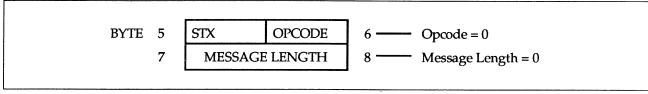

| Figure 5-14 | Terminate Data Collection Instruction Format                              |    |

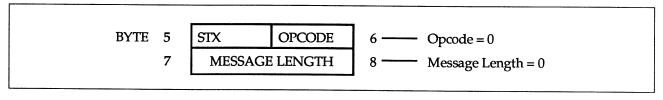

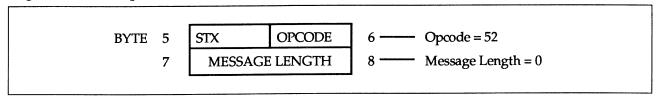

| Figure 5-15 | Terminate Data Collection Response Format (Instruction Executed)95        |    |

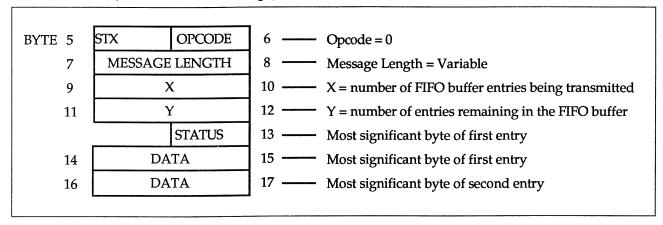

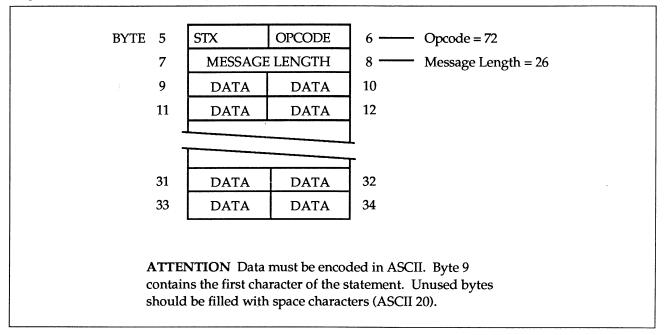

| Figure 5-16 | Read Data Buffer Instruction Format96                                     |    |

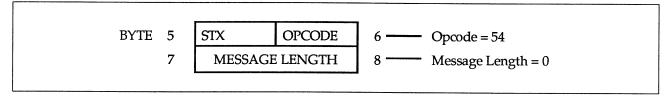

| Figure 5-17 | Read Data Buffer Response Format (Execution Acknowledge)96                |    |

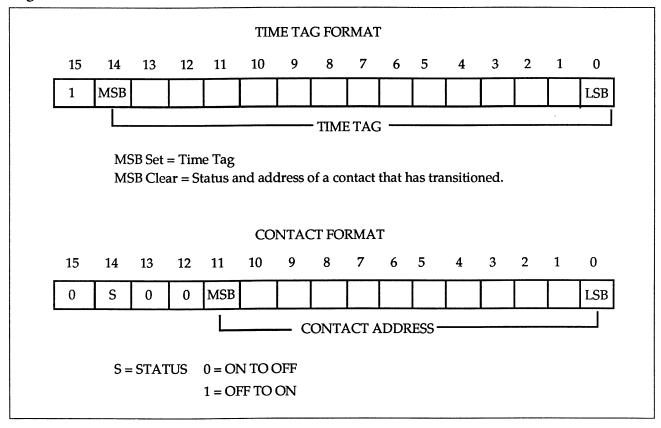

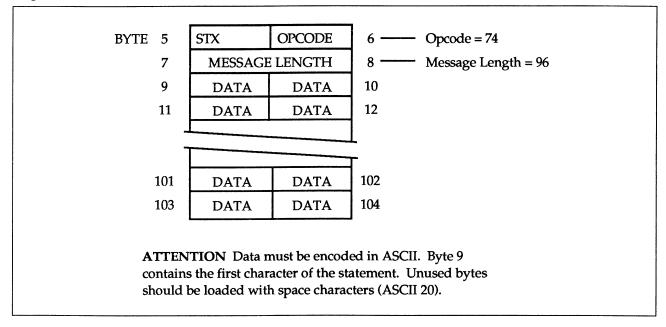

| Figure 5-18 | Data Format for the Read Data Buffer Instruction                          |    |

| Figure 5-19 | Read Mask Table Instruction Format                                        |    |

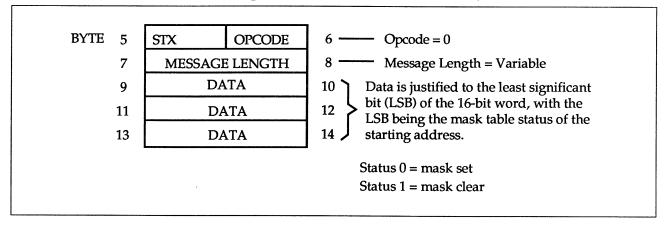

| Figure 5-20 | Read Mask Table Response Format (Instruction Executed)99                  |    |

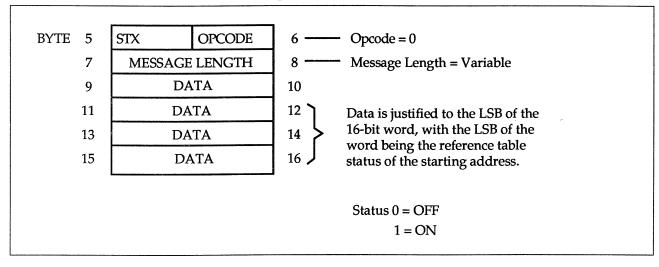

| Figure 5-21 | Read Reference Table Instruction Format (motioscien Excesses)             |    |

| Figure 5-22 | Read Reference Table Response Format (Instruction Executed) 100           |    |

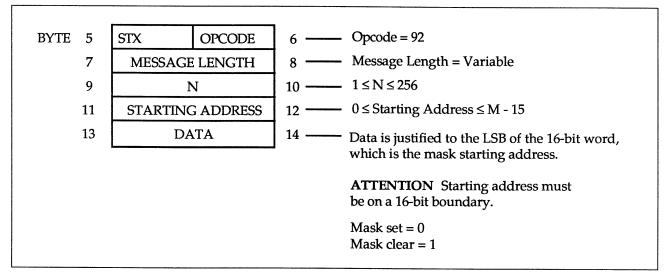

| Figure 5-23 | Write Mask Table Instruction Format101                                    |    |

| Figure 5-24 | Write Mask Table Response Format (Instruction Executed)                   |    |

| Figure 5-24 | Inhibit Mask Table Instruction Format                                     |    |

| Figure 5-25 | Inhibit Mask Table Response Format (Instruction Executed)                 |    |

| Figure 5-27 | Enable Mask Table Instruction Format                                      |    |

| Figure 5-28 | Enable Mask Table Response Format (Instruction Executed)                  |    |

| Figure 5-29 | Read N Registers (No Sign) Instruction Format                             |    |

| ga. 0 0 20  | Continued on nex                                                          | ct |

| E:           | Book N. Bookstone (No. Char). B.                                       |     |

|--------------|------------------------------------------------------------------------|-----|

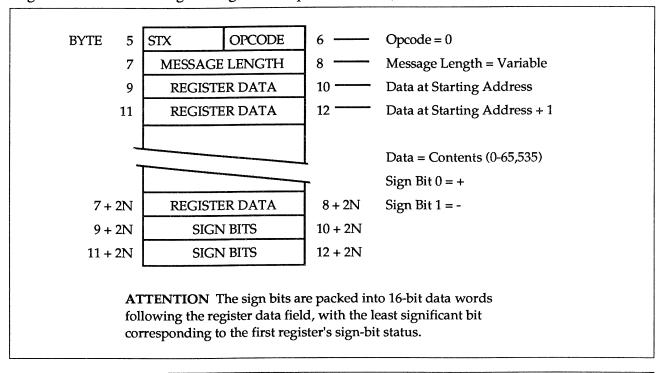

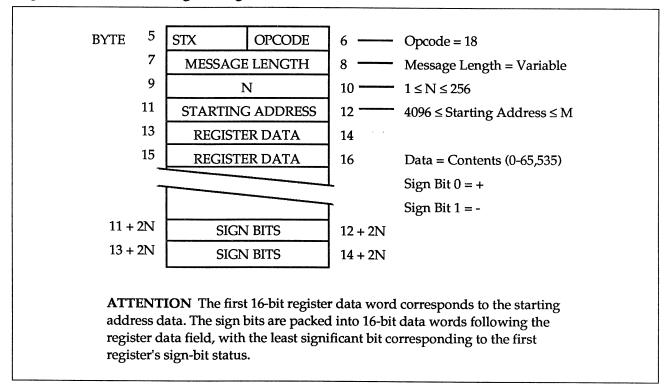

| Figure 5-30  | Read N Registers (No Sign) Response Format (Instruction Executed) 105  |     |

| Figure 5-31  | Read N Signed Registers Instruction Format                             |     |

| Figure 5-32  | Read N Signed Registers Response Format (Instruction Executed) 106     |     |

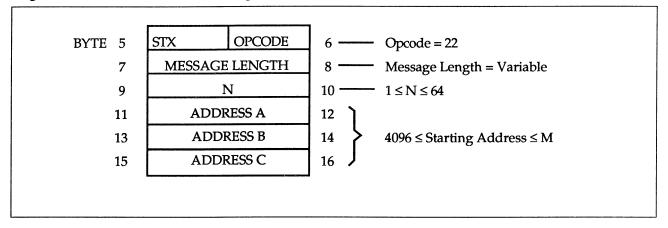

| Figure 5-33  | Read N Scattered Registers Instruction Format                          |     |

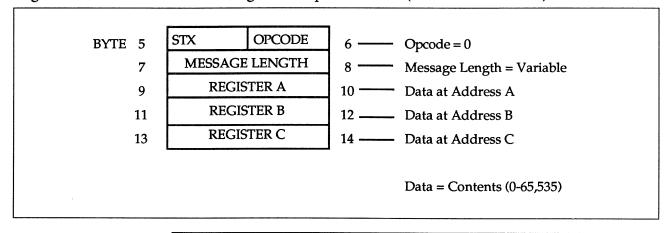

| Figure 5-34  | Read N Scattered Registers Response Format (Instruction Executed) 107  |     |

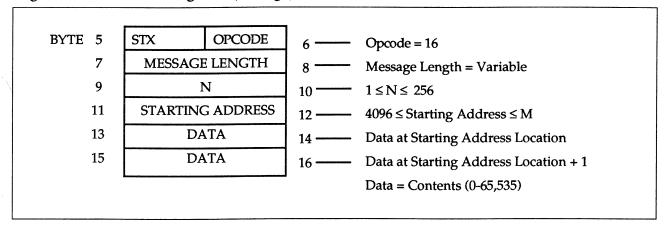

| Figure 5-35  | Write N Registers (No Sign) Instruction Format                         |     |

| Figure 5-36  | Write N Registers (No Sign) Response Format (Instruction Executed) 108 |     |

| Figure 5-37  | Write N Signed Registers Instruction Format 109                        |     |

| Figure 5-38  | Write N Signed Registers Response Format (Instruction Executed) 109    |     |

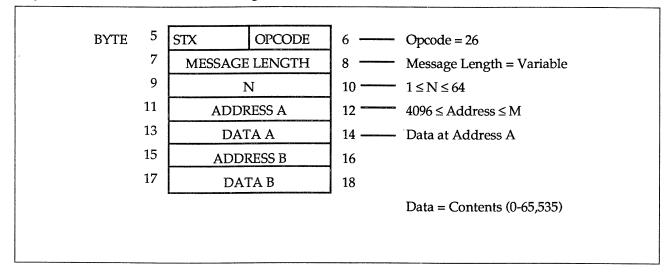

| Figure 5-39  | Write N Scattered Registers Instruction Format                         |     |

| Figure 5-40  | Write N Scattered Registers Response Format (Instruction Executed) 110 |     |

| Figure 5-41  | PULL N I/O Registers Instruction Format                                |     |

| Figure 5-42  | PULL N I/O Registers Response Format (Instruction Executed) 111        |     |

| Figure 5-43  | PUSH N I/O Registers Instruction Format                                |     |

| Figure 5-44  | PUSH N I/O Registers Response Format (Instruction Executed) 112        |     |

| Figure 5-45  | Read N System Status Registers Instruction Format                      |     |

| Figure 5-46  | Read N System Status Registers Response Format                         |     |

| rigure 5-40  | (Instruction Executed)                                                 |     |

| Figure 5-47  | (Instruction Executed)                                                 |     |

|              | Write N System Status Registers Instruction Format                     |     |

| Figure 5-48  | Write N System Status Registers Response Format                        |     |

| Figure F 40  | (Instruction Executed)                                                 |     |

| Figure 5-49  | Request PROGRAM Mode Instruction Format                                |     |

| Figure 5-50  | Request PROGRAM Mode Response Format (Instruction Executed) 116        |     |

| Figure 5-51  | Remove PROGRAM Mode Request Instruction Format                         |     |

| Figure 5-52  | Remove PROGRAM Mode Request Response Format                            |     |

|              | (Instruction Executed)                                                 |     |

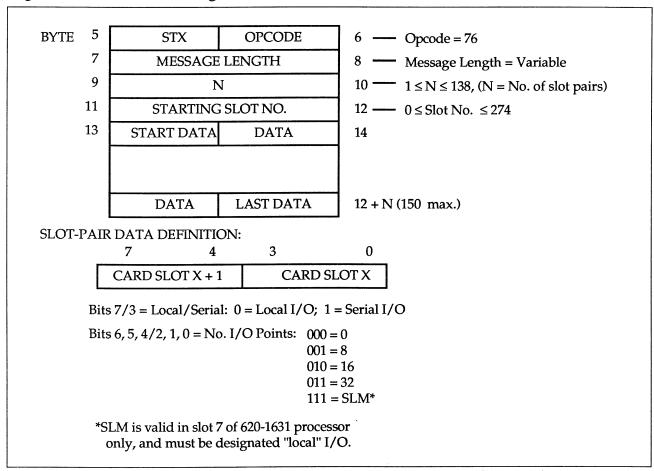

| Figure 5-53  | Write I/O Configuration Instruction Format118                          |     |

| Figure 5-54  | Write I/O Configuration Response Format (Instruction Executed) 119     |     |

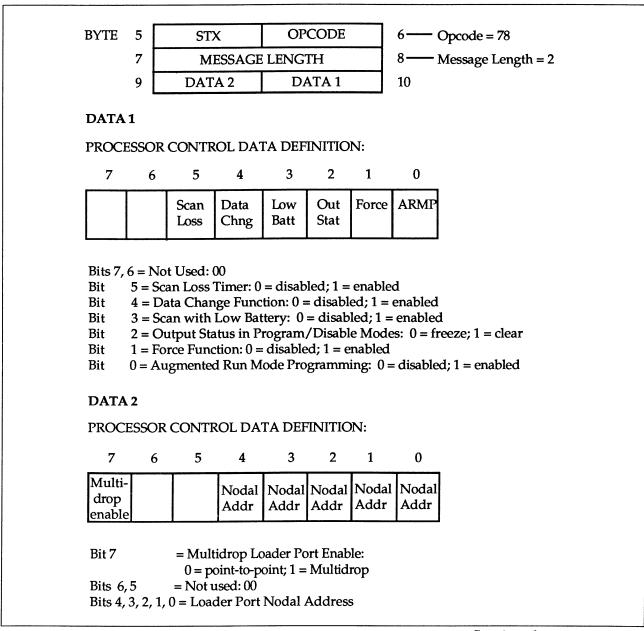

| Figure 5-55  | Write Processor Control Configuration Instruction Format               |     |

| Figure 5-56  | Write Processor Control Configuration Response Format                  |     |

|              | (Instruction Executed)121                                              |     |

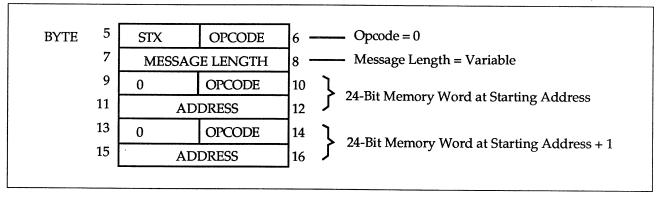

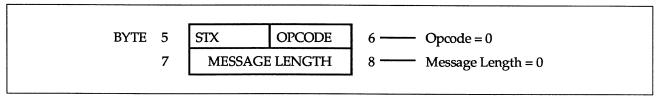

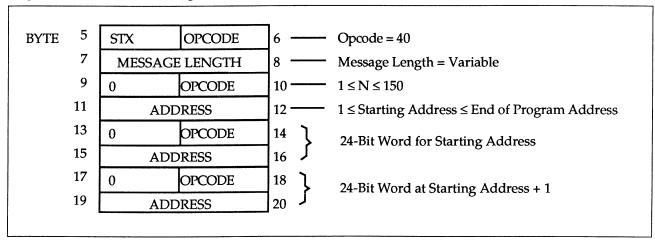

| Figure 5-57  | Upload N Program Memory Words Instruction Format                       |     |

| Figure 5-58  | Upload N Program Memory Words Response Format                          |     |

| -            | (Instruction Executed)                                                 |     |

| Figure 5-59  | (Instruction Executed)                                                 |     |

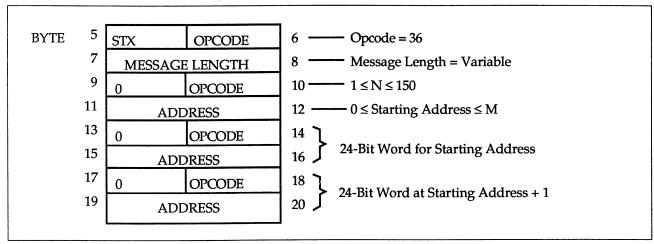

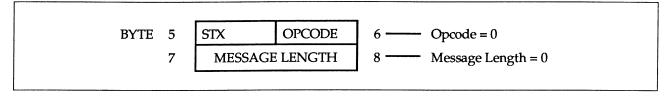

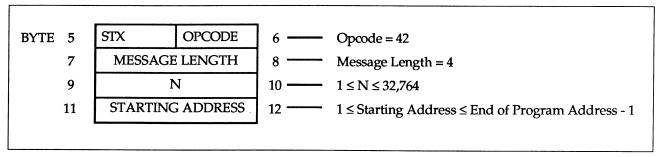

| Figure 5-60  | Download N Program Memory Words Response Format                        |     |

| Ü            | (Instruction Executed)                                                 |     |

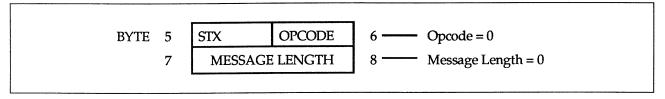

| Figure 5-61  | Clear Program Memory Instruction Format                                |     |

| Figure 5-62  | Clear Program Memory Response Format (Instruction Executed) 125        |     |

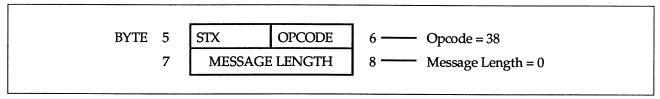

| Figure 5-63  | Insert N Program Memory Words Instruction Format                       |     |

| Figure 5-64  | Insert N Program Memory Words Response Format                          |     |

| <b>3</b>     | (Instruction Executed)                                                 |     |

| Figure 5-65  | Delete N Program Memory Words Instruction Format                       |     |

| Figure 5-66  | Delete N Program Memory Words Response Format                          |     |

| 1 .ga.0 0 00 | (Instruction Executed)                                                 |     |

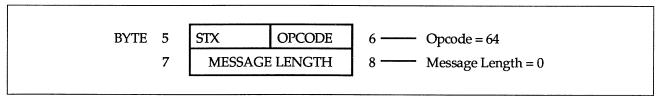

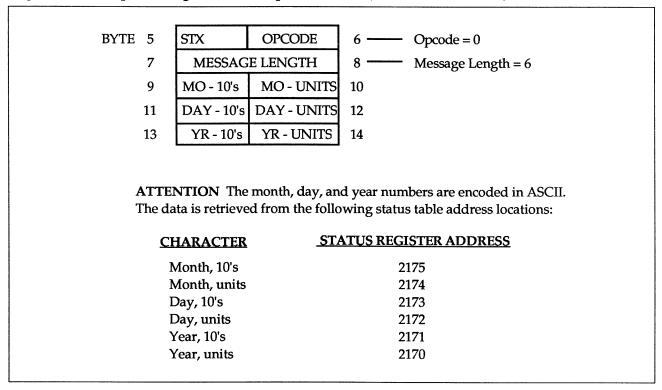

| Figure 5-67  | Upload Program Date Instruction Format                                 |     |

| Figure 5-68  | Upload Program Date Response Format (Instruction Executed)             |     |

| Figure 5-69  | Upload Programmer Instruction Formet                                   |     |

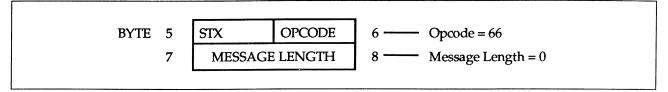

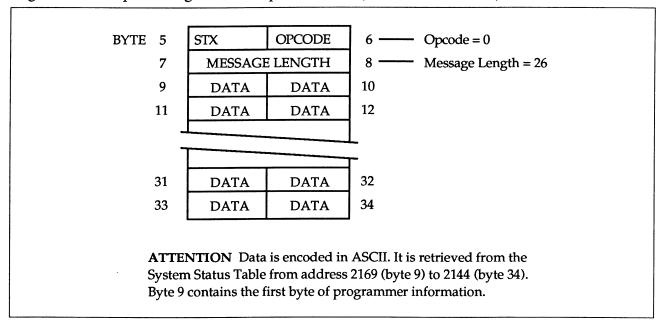

| Figure 5-70  | Upload Programmer Instruction Format                                   |     |

|              | Upload Programmer Response Format (Instruction Executed)               |     |

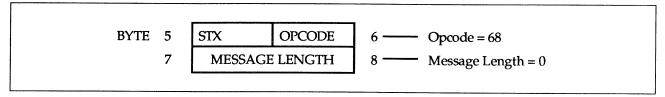

| Figure 5-71  | Upload Title Instruction Format                                        |     |

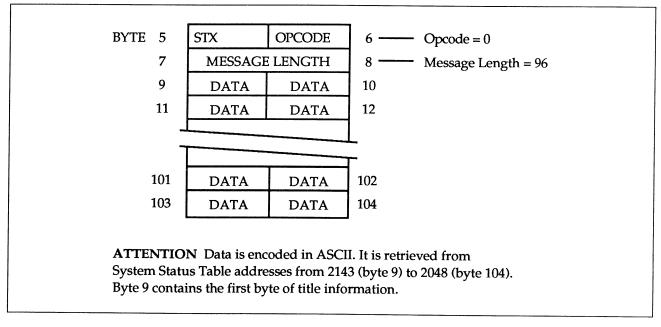

| Figure 5-72  | Upload Title Response Format (Instruction Executed)                    |     |

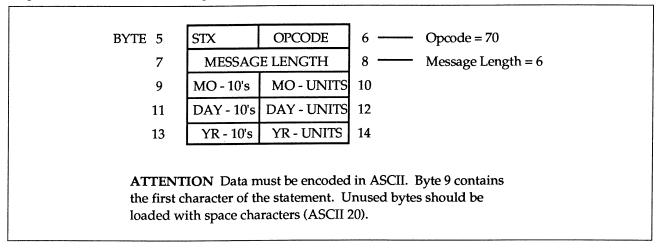

| Figure 5-73  | Download Program Date Instruction Format                               |     |

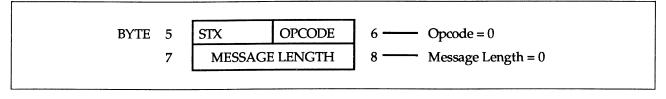

| Figure 5-74  | Download Program Date Response Format (Instruction Executed) 132       |     |

| Figure 5-75  | Download Programmer Instruction Format                                 |     |

| Figure 5-76  | Download Programmer Response Format (Instruction Executed) 133         |     |

| Figure 5-77  | Download Title Instruction Format                                      |     |

| Figure 5-78  | Download Title Response Format (Instruction Executed)                  |     |

|              | Continued on next pag                                                  | ze  |

|              | $r \sim c$                                                             | , . |

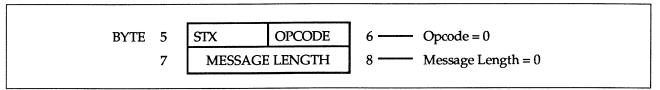

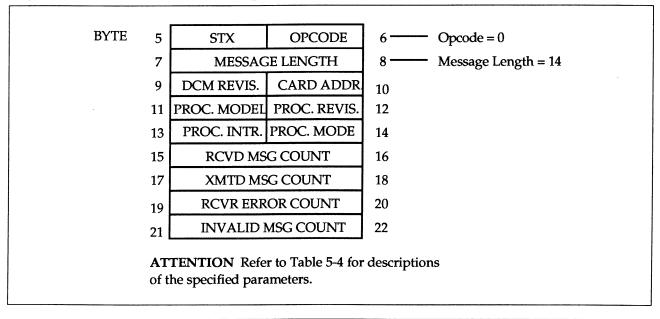

| Figure 5-79 | Read DCM Status Instruction Format                              | 136 |

|-------------|-----------------------------------------------------------------|-----|

| Figure 5-80 | Read DCM Status Response Format (Instruction Executed)          | 136 |

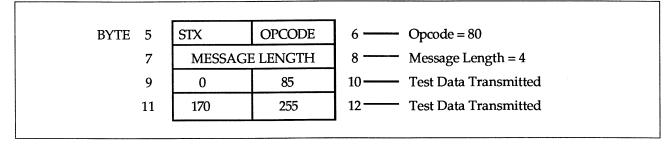

| Figure 5-81 | Loop Back Test Instruction Format                               | 138 |

| Figure 5-82 | Loop Back Test Response Format                                  |     |

| · ·         | (Instruction Received, Data Verified)                           | 138 |

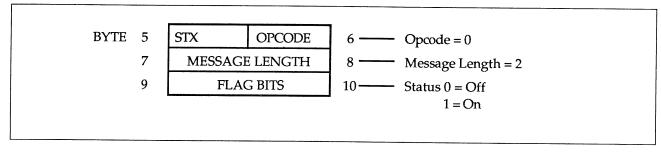

| Figure 5-83 | DCM Flag Mode Response Function                                 | 145 |

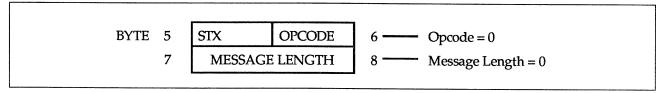

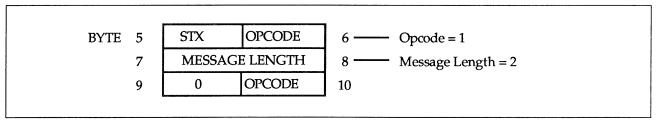

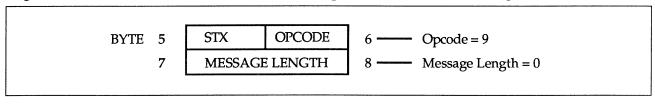

| Figure 5-84 | Invalid Opcode Response Format (Error Message)                  | 147 |

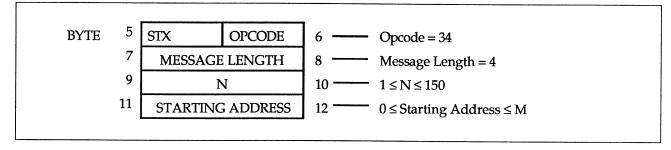

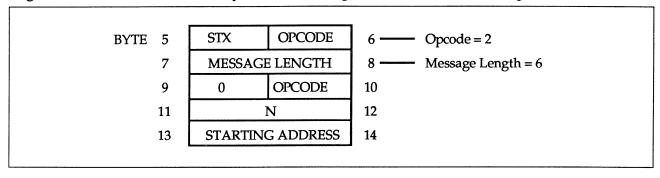

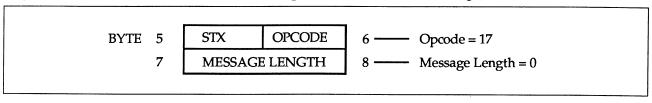

| Figure 5-85 | N Value Exceeds System Limits Response Format (Error Message)   | 148 |

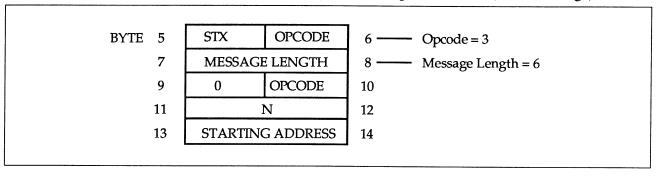

| Figure 5-86 | Starting Address Exceeds Memory Limits Response Format          |     |

|             | (Error Message)                                                 | 149 |

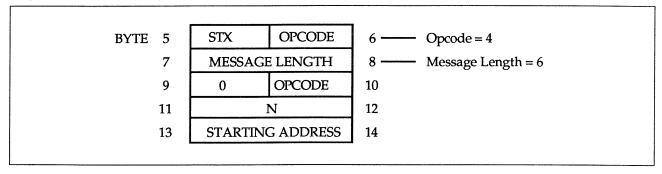

| Figure 5-87 | Memory Block Exceeds Memory Limits Response Format              |     |

| -           | (Error Message)                                                 | 150 |

| Figure 5-88 | Invalid Processor Mode Response Format (Error Message)          | 151 |

| Figure 5-89 | User Program Memory Not Alterable Response Format               |     |

| _           | (Error Message)                                                 | 152 |

| Figure 5-90 | Write Protect Enabled Response Format (Error Message)           | 153 |

| Figure 5-91 | Data Collection in Progress Response Format (Error Message)     | 154 |

| Figure 5-92 | Reference Table Not Initialized Response Format (Error Message) | 155 |

| Figure 5-93 | Processor Access Denied Response Format (Error Message)         | 156 |

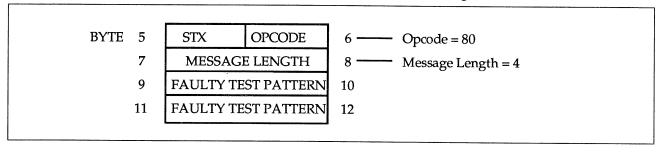

| Figure 5-94 | Invalid Loop Back Test Response Format (Error Message)          | 157 |

| Table 1-1  | 620-0048 and 620-0052 DCM Specifications3                         |

|------------|-------------------------------------------------------------------|

| Table 1-2  | 620-0048 Power Consumption4                                       |

| Table 1-3  | 620-0052 Power Consumption4                                       |

| Table 1-4  | DCM Indicators and Connectors8                                    |

| Table 2-1  | General Procedure for Installing DCM9                             |

| Table 2-2  | DCM Option Slot Locations                                         |

| Table 2-3  | RS422/RS485 Multidrop Network Specifications                      |

|            | DCM Pin Assignments and Reference Designators                     |

| Table 2-4  |                                                                   |

| Table 2-5  | Recommended Cables for DCM RS422/RS485 Operation                  |

| Table 2-6  | Raceway Shielding19                                               |

| Table 2-7  | Tray and Conduit Spacing20                                        |

| Table 3-1  | 620-0048 DCM Parameters and DIP Switches29                        |

| Table 3-2  | Setting 620-0048 DCM Electrical Parameters30                      |

| Table 3-3  | Setting 620-0048 DCM Data Link Parameters                         |

| Table 3-4  | Setting 620-0048 DCM Operational Parameters                       |

| Table 3-5  | 620-0048 DCM SW1 DIP Switch Settings                              |

| Table 3-6  | 620-0048 DCM SW2 DIP Switch Settings - Switches 1, 2, and 3 36    |

| Table 3-7  | 620-0048 DCM SW2 DIP Switch Settings -                            |

| 14510 0 7  | Switches 4, 5, 6, 7, and 8                                        |

| Table 3-8  | 620-0048 DCM SW3 DIP Switch Settings - Switches 1, 2, and 3 39    |

|            |                                                                   |

| Table 3-9  | 620-0048 DCM SW3 DIP Switch Settings - Switches 4, 5, and 6 39    |

| Table 3-10 | 620-0048 DCM SW3 DIP Switch Settings - Switches 7 and 8           |

| Table 3-11 | 620-0052 DCM Parameters and DIP Switches                          |

| Table 3-12 | Setting 620-0052 DCM Electrical Parameters                        |

| Table 3-13 | Setting 620-0052 DCM Data Link Parameters43                       |

| Table 3-14 | Setting 620-0052 DCM Operational Parameters44                     |

| Table 3-15 | 620-0052 DCM SW1 DIP Switch Settings - Switches 1 and 2           |

| Table 3-16 | 620-0052 DCM SW1 DIP Switch Settings - Switches 3 and 4           |

| Table 3-17 | 620-0052 DCM SW2 (for Port 1) and SW4 (for Port 2) DIP Switch     |

|            | Settings - Switches 1, 2, 3, 4, and 5                             |

| Table 3-18 | 620-0052 DCM SW2 (for Port 1) and SW4 (for Port 2) DIP Switch     |

| Table 6 16 | Settings - Switches 6, 7, and 8                                   |

| Table 3-19 | 620-0052 DCM SW3 (for Port 1) and SW5 (for Port 2) DIP Switch     |

| 14016 3-19 | 620-0032 DOM 3W3 (IOI FOIL 1) AND 3W3 (IOI FOIL 2) DIF SWILCH     |

| T-bl- 0 00 | Settings - Switches 1, 2, and 3                                   |

| Table 3-20 | 620-0052 DCM SW3 (for Port 1) and SW5 (for Port 2) DIP Switch     |

| <b></b>    | Settings - Switches 4, 5, 6, 7, and 8                             |

| Table 4-1  | Summary of the Sysgen Process                                     |

| Table 4-2  | DCM Self-Test Sequence53                                          |

| Table 4-3  | Character Functions Used in Header and Text Message Format 60     |

| Table 4-4  | Host Message Types Summary61                                      |

| Table 4-5  | Secondary Message Types Summary                                   |

| Table 4-6  | Flag Bits Used in 620 LCSs72                                      |

| Table 4-7  | Descriptions of Operations in Session Execution Time77-78         |

| Table 4-8  | Checksum Flags and Registers82                                    |

| Table 5-1  | DCM Instructions and Opcodes85                                    |

| Table 5-2  | M and L Values for 620 CPMs86                                     |

| Table 5-2  | Status Byte Definitions for DCM Read Data Buffer Instructions     |

|            |                                                                   |

| Table 5-4  | Descriptions for Read DCM Status Response Parameters              |

| Table 5-5  | Approximate Instruction Execution Times (in Milliseconds) 139-140 |

| Table 5-6  | Request PROGRAM Mode Execution Time                               |

| Table 5-7  | Remove PROGRAM Mode Request Execution Time141                     |

| Table 5-8  | Download N PROGRAM Memory Words Execution Time142                 |

| Table 5-9  | Download N PROGRAM Memory Words Execution Time Calculation        |

|            | Parameters142                                                     |

| Table 5-10 | Insert N PROGRAM Memory Words Execution Time                      |

| Table 5-11 | Insert N PROGRAM Memory Words Execution Time Calculation          |

|            | Parameters                                                        |

|            |                                                                   |

|            | Continued on next page                                            |

| Table 5-12 | Delete N PROGRAM Memory Words Execution Time | 144     |

|------------|----------------------------------------------|---------|

| Table 5-13 | Delete N PROGRAM Memory Words Execution Time | 144     |

| Table 5-14 | Flag Bits for 620 Logic Controller Systems   |         |

| Table 5-15 | Error Messages and Opcodes                   | 146     |

| Table A-1  | DCM Instruction Set Opcodes                  | 160-162 |

| Table A-2  | ASCII-to-Decimal Conversion                  | 165     |

## **Acronyms**

| CPM     | Control Processor Module                          |

|---------|---------------------------------------------------|

|         | Cyclic Redundancy Check                           |

| CS, CTS | Clear-to-Send                                     |

|         | Data Carrier Detect                               |

|         | Data Communications Equipment                     |

| DCM     | Data Collection Module                            |

| DHP     | Data Hiway Port                                   |

| DSR     | Data Set Ready                                    |

| DTE     | Data Terminal Equipment                           |

| DTR     | Data Terminal Ready                               |

| EIA     | Electronic Industries Association                 |

| EMI     | Electromagnetic Interference                      |

| FCC     | Federal Communications Commission                 |

| ICS     | Institute of Computer Science                     |

| IEC     | International Electrotechnical Commission         |

| IEEE    | Institute of Electrical and Electronics Engineers |

| I/O     | Input/Output                                      |

| ISO     | International Standards Organization              |

| LCS     | Logic Controller System                           |

| LED     | Light-Emitting Diode                              |

| NEMA    | National Electrical Manufacturer's Association    |

| PC      | Personal Computer                                 |

| RD      | Receive Data                                      |

| RFI     | Radio Frequency Interference                      |

| RTS, RS | Request-To-Send                                   |

| RXD     | Receive Data                                      |

| SD      | Send Data                                         |

| TXD     | Transmit Data                                     |

| VDE     | Variable Display Equipment                        |

## ATTENTION

ATTENTION: Refer to the *Glossary* (at the back of this manual) for detailed definitions of the following terminology which are used throughout this manual:

- Clear to Send (CTS, CS)

- Data Carrier Detect (DCD, RR)

- Data Set Ready (DSR)

- Data Terminal Ready (DTR)

- Receive Data (RXD, RD)

- Request to Send (RTS, RS)

- Shield Ground

- Signal Ground

- Transmit Data (TXD, SD)

# References

| Publication<br>Title                                                                                      | Publication<br>Number | Binder<br>Title | Binder<br>Number |

|-----------------------------------------------------------------------------------------------------------|-----------------------|-----------------|------------------|

| 620-11/14/16 Logic Controller System<br>User Manual                                                       | 620-8976              | 620 System      | VOLUME I         |

| 620-12/1633/36 Logic Controller<br>System User Manual                                                     | 620-8964              | 620 System      | VOLUME II        |

| 620 Installation and 621 I/O<br>Communications User Manual                                                | 620-8996              | 620 System      | VOLUME I         |

| 620 Installation and 621 I/O<br>Communications for 620-12/1633/36<br>Logic Controller Systems User Manual | 620-8962              | 620 System      | VOLUME II        |

| 621 I/O Specifications User Manual                                                                        | 620-8995              | 620 System      | VOLUME II        |

| 623-60 MS-DOS Loader User Manual                                                                          | 620-8983              | 620 System      | VOLUME VI        |

| 623-6100/6150 Loader/Terminal User<br>Manual                                                              | 623-8940              | 620 System      | VOLUME VI        |

## Section 1 – Data Collection Modules (DCMs)

## Overview

#### Section contents

| Topic                      | See Page |

|----------------------------|----------|

| Overview                   | 1        |

| DCM Functional Description |          |

Function of the 620-0048 & 620-0052 Data Collection Modules (DCM) The 620-0048 and 620-0052 Data Collection Modules (DCMs) are communication interface modules used to connect 620 Logic Controller Systems (LCSs) with general purpose computers.

- The 620-0048 DCM contains one serial interface port that supports data collection.

- The 620-0052 DCM contains two ports:

- port 1 performs data collection functions or general purpose communications interface functions, and

- port 2 performs general communications interface functions.

#### 620-0048 & 620-0052 DCM features

Features of the 620-0048 and 620-0052 DCMs are listed below.

- Both DCMs can be used as general purpose communication interface modules for 620 Logic Controller Systems (LCSs). Any 620 LCS user program memory contents, input/output status, data registers, or system register contents may be examined or modified through the DCM. The DCM provides this access for other services beyond the capabilities of the programmable controller.

- Each DCM provides low- to medium-speed connection of a 620 LCS to another computing device. Each port implements Honeywell's asychronous byte count (ABC) protocol, which provides a simple, easy-to-implement interface to any 620 LCS. The ABC protocol is suitable for use in both point-to-point and multidrop network applications. Data transparency is achieved through a byte count procedure that eliminates the need for a special data encoding for character insertion and deletion.

- Each DCM port can operate as a front-end communication processor to the 620 LCS. In this capacity each port performs computer interface functions between a host computer and the 620 LCS. Both ports on the 620-0052 can be used for communication interface, thereby providing the functionality of two communications interfaces within a single module width.

- The serial ports of both DCMs are capable of asynchronous data transmission. Internal timing generation provides communication at standard I/O rates of 110, 300, 600, 1200, 2400, 4800, 9600, and 19.2K baud.

- Each DCM port interfaces to a host device in conformance to the electrical characteristics of EIA Standards RS232 and RS422/RS485. The electrical interface is capable of either half- or full-duplex circuit operation.

- Point-to-point wiring is possible with each type of electrical interface. Multipoint operation is possible in these cases:

- RS232 interface and modem suitable for multipoint operation are used.

- RS422/RS485 interface is used with or without a modem.

# Overview, Continued

620-0048 and 620-0052 DCM specifications Refer to Table 1-1 for general specifications for the 620-0048 and 620-0052 DCMs.

Table 1-1 620-0048 and 620-0052 DCM Specifications

| Item                                  | Specification                                                                                     |

|---------------------------------------|---------------------------------------------------------------------------------------------------|

| Operating Temperature                 | 0°C to 60°C (32°F to 140°F)                                                                       |

| Storage Temperature                   | -40°C to 85°C (-40°F to 185°F)                                                                    |

| Humidity                              | 0 to 95% (noncondensing)                                                                          |

| Dimensions                            | 26.7 x 3.05 x 16.51 cm (10.5 x 1.2 x 6.5 inches)                                                  |

| Weight                                | 0.49 kg (1.1 lbs)                                                                                 |

| IEC 68-2-6 Test FC<br>Frequency Range | 10 to 150 Hz                                                                                      |

| Vibration Amplitude                   | 0.006 inches (0.15 mm) peak-to-peak from 10 to 57 Hz, 1 G constant acceleration from 57 to 150 Hz |

| Showering Arc Test                    | NEMA-ICS-1-109                                                                                    |

| FCC Rulings on<br>Emitted RFI         | Docket #20780 Part #15                                                                            |

| IEEE Surge Withstand<br>Standard      | #587-1080                                                                                         |

| Honeywell Noise Test                  | VDE-0871 Class A                                                                                  |

## Overview, Continued

## Power supply loading

Refer to Table 1-2 for the power supply consumption for the 620-0048 DCM and Table 1-3 for the power supply consumption for the 620-0052 DCM.

Table 1-2 620-0048 Power Consumption

| 1            | 520-0048<br>VER SUPPLY       | I (TYPICAL) | I (MAXIMUM) |

|--------------|------------------------------|-------------|-------------|

| 5V           |                              | 1.3A        | 1.5A        |

| +12V<br>-12V | 620-20/25<br>620-30/35       | 60mA        | 100mA       |

| +15V<br>-15V | 620-06/10/15<br>620-11/14/16 | 60mA        | 100mA       |

|              | 620-12<br>620-1633<br>620-36 | 60mA        | 100mA       |

Table 1-3 620-0052 Power Consumption

|              | 520-0052<br>VER SUPPLY       | I (TYPICAL) | I (MAXIMUM) |

|--------------|------------------------------|-------------|-------------|

| 5V           |                              | 1.6A        | 1.8A        |

| +12V<br>-12V | 620-20/25<br>620-30/35       | 74mA        | 90mA        |

| +15V<br>-15V | 620-06/10/15<br>620-11/14/16 | 74mA        | 90mA        |

|              | 620-12<br>620-1633<br>620-36 | 74mA        | 90mA        |

## Overview, Continued

# RS232 electrical specifications

All signals compatible to RS232 adhere to EIA RS232C standard (Section 2 – *Electrical Signal Charactersitics*) specifications.

# RS422/RS485 electrical specifications

All signals compatible to RS422A/RS485 adhere to EIA RS422A/RS485 standard spcifications. The following additional specifications apply to support multidrop operation:

- common mode output voltage line drivers: -7V, +12V,

- tristate control through RTS (RS) on SD line driver,

- thermal shutdown protection on line drivers,

- positive and negative current limiting (line drivers),

- input impedance of line receivers: 12K ohms minimum, and

- 150-ohm line termination on RD, CS, RR receivers (RD selectable).

#### **ATTENTION**

ATTENTION: Refer to the *Glossary* (at the back of this manual) for detailed definitions of the following terminology which are used throughout this manual:

- Clear to Send (CTS, CS)

- Data Carrier Detect (DCD, RR)

- Data Set Ready (DSR)

- Data Terminal Ready (DTR)

- Receive Data (RXD, RD)

- Request to Send (RTS, RS)

- · Shield Ground

- · Signal Ground

- Transmit Data (TXD, SD)

# **DCM Functional Description**

## DCM frontplate

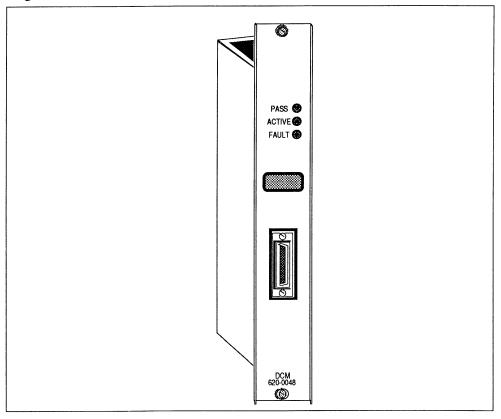

Figure 1-1 shows the frontplate of the 620-0048 DCM and Figure 1-2 shows the frontplate of the 620-0052 DCM.

Figure 1-1 620-0048 DCM Frontplate

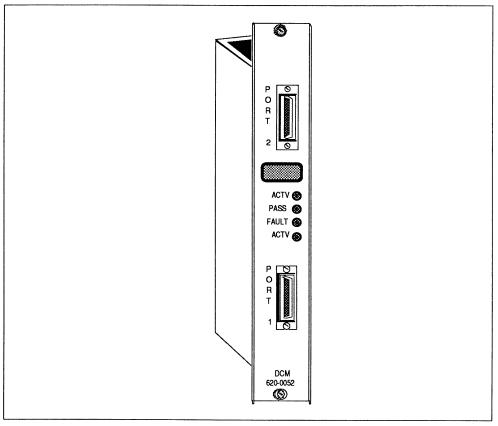

# **DCM Functional Description**

**DCM frontplate,** continued

Figure 1-2 620-0052 DCM Frontplate

## DCM Functional Description, Continued

# Indicators and connectors

The DCM frontplate indicators and connectors are used to view certain operating conditions and to set up the DCM for proper operation. There are three LED status indicators on the frontplate of the 620-0048 DCM and four status indicators on the frontplate of the 620-0052 DCM. Table 1-4 describes the indicators and connectors on the frontplate of each module

Table 1-4 DCM Indicators and Connectors

| Indicator/Connector        | Description                                                                                                                                                                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status LEDs • PASS (green) | Lit when the module self-test is successfully completed at processor power-up.                                                                                                                                                                         |

| ACTIVE (green)             | Lit during the reception and transmission of a message through the port.                                                                                                                                                                               |

| • FAULT (red)              | Lit prior to the DCM establishing communications with the 620 LCS and whenever the DCM loses communications with the 620 LCS.  ATTENTION The FAULT LED also lights if the DCM fails its diagnostic test.                                               |

| DTE Port(s)                | 25-pin D-series subminiature receptacle connectors (AMP HDP-20 series metal shell connectors equipped with an AMP 206512-1 locking post assembly) that serve as serial ports that are switch-selectable for either RS232 or RS422/RS485 compatibility. |

## Section 2 - DCM Installation

## **Overview**

#### **Section contents**

| Торіс                     | See Page |

|---------------------------|----------|

| <br>Overview              | 9        |

| Installing the DCM Module | 10       |

| Network Installation      | 11       |

| DCM Wiring                | 17       |

## Installation procedure

To install a DCM module, follow the general procedure outlined in Table 2-1.

Table 2-1 General Procedure for Installing DCM

| Step | Action                                 | Procedure Reference                          |

|------|----------------------------------------|----------------------------------------------|

| 1    | Install network cabling.               | Network Installation – see page 11.          |

| 2    | Install DCM wiring.                    | DCM Wiring – see page 17.                    |

| 3    | Set appropriate DIP switches.          | Section 3 — DCM Configuration — see page 27. |

| 4    | Install DCM in 620 LCS processor rack. | Installing the DCM Module — see page 10.     |

## Installing the DCM Module

# DCM option slot locations

The 620-0048 and 620-0052 DCMs are single-slot modules that must be placed in an appropriate option slot of a 620 LCS. Refer to Table 2-2 for the various processors and processor racks and the positions available for option modules.

Table 2-2 DCM Option Slot Locations

| Processor      | Processor Rack | Option Slots  |

|----------------|----------------|---------------|

| 620-06/10/15   | 620-0090/0091  | М             |

| 620-11/14/1631 | 620-1690/1693  | K or L        |

|                | 620-1690/1693  | K or L        |

| 620-12/1633/36 | 620-3691       | I, J, K, or L |

| 620-20/25      | 620-2590       | A or B        |

| 620-30/35      | 620-3590       | A, B, C, or D |

### **ATTENTION**

ATTENTION: Before installing the DCM in the 620 LCS processor rack, make sure that:

- network cabling is properly installed (refer to Network Installation);

- DCM wiring is properly installed and ready to be connected to the DCM communications port (refer to DCM Wiring); and

- DCM DIP switches have been properly set (refer to Section 3 DCM Configuration).

## **Network Installation**

### **DCM** configurations

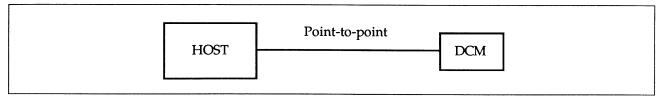

There are two types of configurations for interconnecting DCM(s) to a host. A point-to-point connection is between only two points (see Figure 2-1).

Figure 2-1 Point-to-Point Configuration

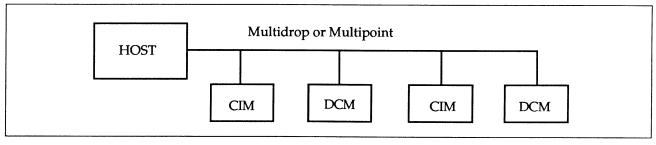

A multipoint/multidrop configuration connects three or more points on a common line; there is a single master and series of slaves (see Figure 2-2).

Figure 2-2 Multipoint/Multidrop Configuration

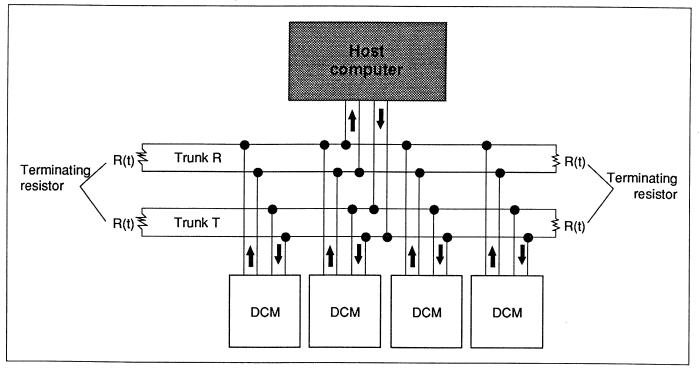

#### Twisted-pair networking

The DCM is designed with an RS422/RS485 multidrop compatible serial port, therefore it is possible to configure a multidrop network without modems. Refer to Table 2-3 for RS422/RS485 multidrop network specifications.

Table 2-3 RS422/RS485 Multidrop Network Specifications

| Item                  | Specification                                         |  |

|-----------------------|-------------------------------------------------------|--|

| Maximum Population    | 32 DCM port connections per networ trunk              |  |

| Maximum Trunk Length  | Cable dependent                                       |  |

| Maximum Branch Length | 61 cm (2 feet)                                        |  |

| Data Rate             | 110, 300, 600, 1200, 2400, 4800, 9600, and 19.2K baud |  |

# Twisted-pair network topology

The twisted-pair network topology accommodates a maximum of thirtytwo, two-foot branches extending from the network trunk to the DCM. The branches may be located at any point along the network trunk without restrictions on distance between branches.

Multidrop networking of DCMs to a host can be implemented with either single or two-twisted pair cable.

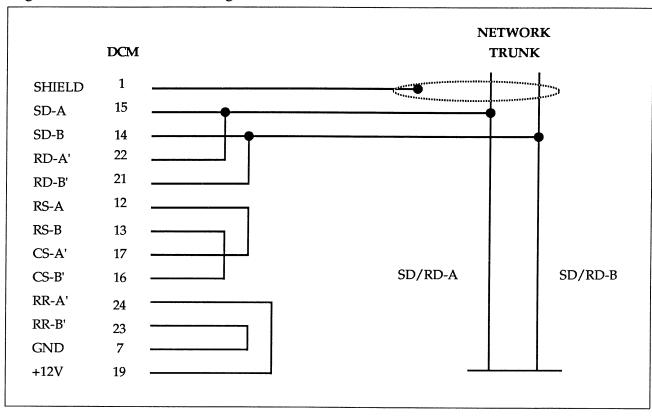

- Refer to Figure 2-8 (in *DCM Wiring Diagrams*) for the basic single twisted-pair topology. The network trunk consists of a single twisted-pair cable. The cable serves as an output line for host transmissions to the DCMs and as an input line for DCM response transmissions to the host.

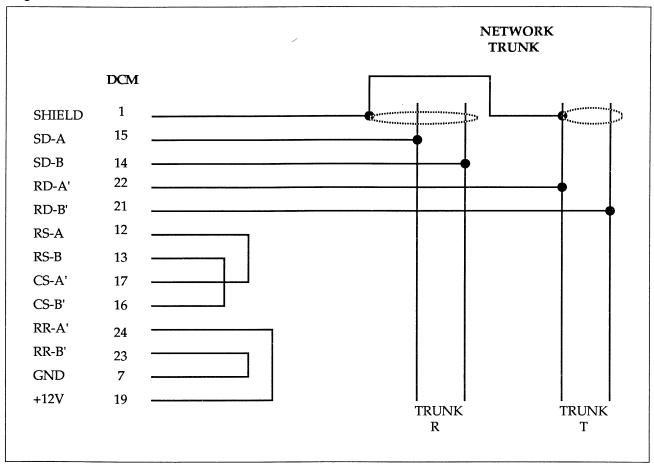

- Refer to Figure 2-9 (in DCM Wiring Diagrams) for the basic two

twisted-pair network topology. The network trunk consists of two

twisted-pair cables. Trunk T serves as an output line for host

transmission to the DCMs and Trunk R serves as an input line for DCM

response transmissions to the host.

# RS422 multidrop connection

The RS422/RS485 serial interface is designed to be attached to the trunk line of a multidrop twisted-pair network. The network trunk may be either a single twisted-pair network or a two-twisted pair cable. Operating a single twisted-pair network rather than a point-to-point requires the following:

- 1. The host Send Data (SD) line driver must be configured to switch into the tristate mode when its serial interface is not in the transmit mode. To do this, connect the tristate control of the SD line driver to the Request to Send signal. Refer to Figure 3-2 (in Section 3) for an example circuit diagram as implemented by the DCM.

- 2. The Receive Data (RD) line receiver must have its termination resistor switch open except at the ends of a multidrop trunk line. In the point-to-point mode, the RD receiver is one end of a line, therefore the termination resistor switch must be closed. Refer to Figure 3-3 for the location of the termination resistor.

The connection of the RS422/RS485 interface to a modem (DCE) which operates on a multidrop network is actually a point-to-point connection from the DTE standpoint. The line configuration switch (SW1, switch 1 for 620-0048 DCMs; SW2 switch 7 for 620-0052 DCMs port 1; and SW4 switch 7 for 620-0052 DCMs port 2 — refer to Section 3 for specific details on setting DCM DIP switches) should be set for multidrop, so that the DCM operates in a half-duplex mode.

DCM pin assignments and reference designators

Refer to Table 2-4 for DCM pin assignments and reference designators.

Table 2-4 DCM Pin Assignments and Reference Designators

| Pin Number | Signal (I/O Description)          | Connector Designator | Interface Type    |

|------------|-----------------------------------|----------------------|-------------------|

| 1          | Shield                            |                      |                   |

| 2          | Transmit Data (Output)            | TXD                  | RS232             |

| 3          | Receive Data (Input)              | RXD                  | RS232             |

| 4          | Request to Send (Output)          | RTS                  | RS232             |

| 5          | Clear to Send (Input)             | CTS                  | RS232             |

| 6          | Data Set Ready (Input)            | DSR                  | RS232             |

| 7          | Signal Ground                     |                      |                   |

| 8          | Data Carrier Detect (Input)       | DCD                  | RS232             |

| 9          | Not used                          |                      |                   |

| 10         | -12V through 1K                   | -12V                 | RS232             |

| 11         | Not used                          |                      |                   |

| 12         | Request to Send (Output)          | RS-A                 | RS422/RS485       |

| 13         | Request to Send, Inv.             | RS-B                 | RS422/RS485       |

| 14         | Transmit Data, Inv. (Output)      | SD-B                 | RS422/RS485       |

| 15         | Transmit Data                     | SD-A                 | RS422/RS485       |

| 16         | Clear to Send, Inv. (Input)       | CS-B'                | RS422/RS485       |

| 17         | Clear to Send                     | CS-A'                | RS422/RS485       |

| 18         | Not used                          |                      |                   |

| 19         | +12V through 1K                   | +12V                 | RS232/RS422/RS485 |

| 20         | Data Terminal Ready (Output)      | DTR                  | RS232             |

| 21         | Receive Data, Inv. (Input)        | RD-B'                | RS422/RS485       |

| 22         | Receive Data                      | RD-A'                | RS422/RS485       |

| 23         | Data Carrier Detect, Inv. (Input) | RR-B'                | RS422/RS485       |

| 24         | Data Carrier Detect               | RR-A'                | RS422/RS485       |

| 25         | Not used                          |                      |                   |

#### Network trunk cable

The network trunk cable must be routed past the 620 LCS. Branches from the network trunk connect the DCM to the trunk and are limited to 2 feet (0.6m) in length. The branch cable may be the same type as the trunk or a less rigid type of the same quality (for example, Belden 9182 for the network trunk and Belden 9729 for the branches).

#### Cable selection

When selecting data communications cable, observe the following guidelines:

- 1. Either two single twisted-pair cables or one two-pair cable must be used for two twisted-pair networks.

- 2. Individual shielding of each pair is recommended.

- 3. Characteristic cable impedance  $\geq$  100 ohms.

- 4. Network trunk must be properly terminated.

- 5. Construction that meets local building codes.

# Calculating network trunk length

The length of the network trunk is limited by the characteristics of the cable. Use the following equation to calculate the length of the network trunk for a specific cable.

Maximum Trunk Length (feet) =  $(Z/R) \times 1000$

where:

Z = Cable characteristic impedance (ohms)

R = Cable conductor resistance per 1000 feet (ohms)

Example: Belden 9182 cable

Z = 150 ohmR = 14 ohms

Maximum Trunk Length =  $(150 \text{ ohms}/14 \text{ ohms}) \times 1000 = 10,714 \text{ feet}$

Example: Belden 9729 cable

Z = 100 ohmsR = 24 ohms

Maximum Trunk Length =  $(100 \text{ ohms/}24 \text{ ohms}) \times 1000 = 4166 \text{ feet}$

#### **Network termination**

Resistors must be attached at each end of each pair of the network trunk cable. Two resistors are required for single pair networks and four are required for two-pair networks. The resistor value must be equal to twice the characteristic impedance of the network trunk cable for the above equations to apply. The resistor power rating should be 1/8-watt or greater.

Example: Belden 9182 cable

Z = 150 ohms Terminating resistors = 300 ohms

#### Cable identification

The network trunk may consist of one or two twisted-pair cables. Cable manufacturers color-code multipair cable to aid in the identification of conductors. Identify the cable conductors to network function before installation.

## **DCM Wiring**

#### **General considerations**

Observe these considerations when installing the DCM:

- Maintain a 60°C (140 °F) or less ambient air temperature at the bottom of each 620 LCS rack assembly.

- Separate all 440VAC (or higher) electrical supply lines as far from 620 LCS components as is practical.

- Run all 440VAC lines in separate conduit from I/O wiring ducts.

- Separate AC and data wiring as far as is practical.

- Install all wiring according to IEEE Standard 518.

- Cross two cables carrying different types of signals (data versus power) at a right angle rather than running them parallel for any distance.

- Terminate all cables at both ends, excluding the shield. If a termination is not made or is intermittent, noise immunity is lost even though the system may transmit valid data.

- Ensure that the entire Communications Network System is grounded to earth ground. The maximum ground reference voltage is 5 volts.

- Shield continuity must be maintained. Ensure that shield leads are not broken.

- Route cables around rather than through high noise areas.

- Allow the minimum amount of unshielded wire that will accommodate connection.

- Route shielded data cable along grounded surfaces such as metal cabinet walls and in conduit or trays. Single shield cable is most effective when routed along grounded surfaces.

- Configurations implementing the RS232 interface require multiple connector cable rated for data transmission.

# General considerations, continued

• Configurations implementing RS422/RS485 interface require individually shielded twisted-pair cable with a characteristic impedance of 100 ohms or greater. Refer to Table 2-5 for recommended cables.

Table 2-5 Recommended Cables for DCM RS422/RS485 Operation

|                     | Belden | Alpha |

|---------------------|--------|-------|

| Single Twisted-Pair | 9182   | 9823  |

| Two Twisted-Pair    | 9729   |       |

| Three Twisted-Pair  | 9730   | 6073  |

#### Conduit shielding

Conduit or cable trays are used to route the network trunkline within the plant, for short distances or for several miles. Often the same conduit is used to carry both data and power wiring, creating a problem with electromagnetic interference. The choice of materials and configuration for the cable conduit can determine the degree of protection from this interference.

Refer to Table 2-6, which is taken from IEEE Standard 518 for the installation of electrical equipment, to compare different types of conduits and raceways for magnetic field attenuation at 60 Hz and for electrostatic attenuation at 100 KHz.

Table 2-6 Raceway Shielding

|                                                                              | Thickness                                 | 60 Hz Magn<br>Attenu  |                      | 100 KHz E<br>Field Atte       |                      |

|------------------------------------------------------------------------------|-------------------------------------------|-----------------------|----------------------|-------------------------------|----------------------|

| Raceway Shielding                                                            | mm (inches)                               | Ratio                 | dB                   | Ratio                         | dB                   |

| Free air<br>2-inch aluminum conduit<br>#16 gauge aluminum tray               | 3.91 (.154)<br>1.52 (.060)                | 1:1<br>1.5:1<br>1.6:1 | 0<br>3.3<br>4.1      | 1:1<br>2150:1<br>15500:1      | 0<br>66.5<br>83.9    |

| #16 gauge aluminum tray<br>#16 gauge galv. ingot iron<br>tray                | 1.52 (.060)<br>1.52 (.060)                | 3:1<br>3.2:1          | 9.4<br>10.0          | 20000:1<br>22000:1            | 86.0<br>86.8         |

| 2-inch IPS copper pipe<br>#16 gauge aluminum tray<br>#14 gauge aluminum tray | 3.96 (.156)<br>1.52 (.060)<br>1.90 (.075) | 3.3:1<br>4.2:1<br>6:1 | 10.2<br>11.5<br>15.5 | 10750:1<br>29000:1<br>23750:1 | 80.6<br>89.3<br>87.5 |

| 2-inch metallic tubing<br>2-inch rigid galv. conduit                         | 1.65 (.065)<br>3.91 (.154)                | 6.7:1<br>40:1         | 16.5<br>32.0         | 3350:1<br>8850:1              | 70.5<br>78.9         |

#### Cable spacing

As far as is practical, it is advised to separate noise-creating sources (such as those with time-varying voltage or time-varying current) from data signal cables. Group cables with similar levels of noise susceptibility together, and group those with similar levels of noise generation separately in trays and conduits.

IEEE defines the following four classes of wiring that differ in signal level and noise susceptibility:

- Data 1 high noise susceptibility; analog signals of less than 50V and digital signals of less than 15V.

- Data 2 medium susceptibility; analog signals greater than 50V and switching circuits.

- Data 3 low susceptibility; switching signals greater than 50V, analog signals greater than 50V, regulating signals of 50V with currents less than 20A; AC feeders less than 20A.

- Power AC and DC buses of 0-1000V with currents of 20-800A.

#### Tray spacing

Refer to Table 2-7 for the recommended minimum distances between the top of one tray and the bottom of the tray above, or between sides of adjacent trays. Table 2-7 also lists the recommended distances between trays and conduits.

Table 2-7 Tray and Conduit Spacing

| Cable<br>Class | Tray<br>Spacing<br>cm (inches) | Tray-Conduit<br>Spacing<br>cm (inches) | Conduit<br>Spacing<br>cm (inches) |

|----------------|--------------------------------|----------------------------------------|-----------------------------------|

| Data 1         | 0                              | 0                                      | 0                                 |

| Data 2         | 0                              | 2.5 (1)                                | 2.5 (1)                           |

| Data 3         | 15.2 (6)                       | 10.1 (4)                               | 7.6 (3)                           |

| Power          | 66.0 (26)                      | 45.7 (18)                              | 30.5 (12)                         |

#### Tray considerations

Refer to the following considerations when installing trays:

- When separate trays are impractical, Data 1 and 2 cables may be placed in the same tray, provided they are separated by a grounded steel barrier.

- Trays containing Data 1 and 2 cabling should have solid bottoms and tray covers to provide complete shielding.

- Ventilation slots or louvers may only be used in trays containing Data 3 cables.

#### Grounding

Adequate grounding is important for safety considerations and to reduce electromagnetic noise interference. A grounding path for the system components and enclosures should be provided. This ground is connected to the central ground for all electrical equipment and AC power within the user's facility (that is, earth ground). All earth ground connections must be permanent and provide a continuous low-impedance path to earth ground for induced noise currents and fault currents.

System ground is accomplished by the mounting hardware. A rack assembly grounding screw (optional) is provided with each chassis for customer use to connect the system components to earth ground. Local electrical codes must be observed when installing a DCM Network System. Refer to the 620 Installation and 621 I/O Communications User Manual, the 620 Installation and 621 I/O Communications for 620-12/1633/36 Logic Controller Systems User Manual, or the 620-12/1633/36 Logic Controller System User Manual, as appropriate, for more information on grounding.

DCM wiring diagrams

Refer to Figures 2-3 through 2-9 for network wiring information for all DCM configurations.

Figure 2-3 RS232 Connection to Full Function Modem

| D       | M       | MODEM   |

|---------|---------|---------|

| SHIELD  | 1       | SHIELD  |

| TXD     | 2       | TXD     |

| RXD     | 3       | RXD     |

| RTS     | 4 ————  | RTS     |

| CTS     | 5 ————  | CTS     |

| DSR     | 6       | DSR     |

| SIG GND | 7 ————  | SIG GND |

| DCD     | 8       | DCD     |

| DTR     | 20 ———— | DTR     |

Figure 2-4 RS232 Connection to Minimum Function Modem

DCM wiring diagrams, continued

Figure 2-5 RS232 Connection to Host

Figure 2-6 RS422/RS485 Connection to Minimum Function Modem

DCM wiring diagrams, continued

Figure 2-7 RS422/RS485 Connection to Host

### DCM Wiring, Continued

DCM wiring diagrams, continued

Figure 2-8 RS422/RS485 Single Twisted-Pair Network Connection

# DCM Wiring, Continued

DCM wiring diagrams, continued

Figure 2-9 RS422/RS485 Two Twisted-Pair Network Connection

### Section 3 – DCM Configuration

### **Overview**

#### **Section contents**

| Topic                            | See Page |

|----------------------------------|----------|

| Overview                         | 27       |

| 620-0048 DCM DIP Switch Settings |          |

| 620-0052 DCM DIP Switch Settings | 40       |

#### **Background**

Certain parameters must be considered when the DCM is interfaced with a host computer. Selection of various options in each category allows you to configure the DCM to your particular application. Options are selected by means of DIP switch settings. Designate the DCM parameters by setting the DIP switches according to the procedures presented in this section for either the 620-0048 or 620-0052 DCM.

### 620-0048 DCM DIP Switch Settings

# Setting 620-0048 DCM DIP switches

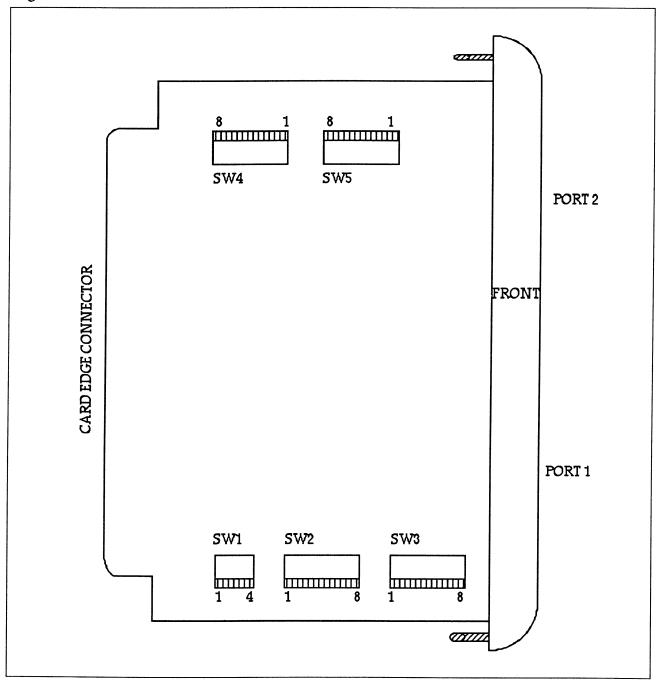

The single printed circuit board of the 620-0048 DCM is keyed to a receptive backplane. Three banks of DIP switches located on the lower edge of the module circuit board provide 20 DIP switches that control the DCM configuration. There are two 8-position and one 4-position DIP switch packs located on the module board as shown in Figure 3-1.

SW3 SW2 SW1

Switch 1 Switch 8

Figure 3-1 620-0048 DCM DIP Switches

620-0048 DCM parameters

Refer to Table 3-1 for a list of the parameters and their controlling DIP switches to be considered when interfacing the 620-0048 DCM with a host computer.

Table 3-1 620-0048 DCM Parameters and DIP Switches

| Parameter                                                                | DIP Switch               |

|--------------------------------------------------------------------------|--------------------------|

| RS422 Receiver Termination                                               | SW1 switch 1             |

| Point-to-Point/Multipoint Select                                         | SW1 switch 2             |

| RS232 or RS422/RS485<br>Transmission                                     | SW1 switch 3             |

| One Stop Bit/Two Stop Bits                                               | SW1 switch 4             |

| Accept/Reject Instructions that Write to Program Memory                  | SW2 switch 1             |

| Accept/Reject Instructions that Write to the Control Output Status Table | SW2 switch 2             |

| Normal Operation/Flag Mode                                               | SW2 switch 3             |

| Nodal Address Select                                                     | SW2 switches 4 through 8 |

| Baud Rate                                                                | SW3 switches 1 through 3 |

| Parity Bit Enable/Disable                                                | SW3 switch 4             |

| Even/Odd Parity                                                          | SW3 switch 5             |

| Spare                                                                    | SW3 switch 6             |

| Module Address Select                                                    | SW3 switches 7 and 8     |

# Setting 620-0048 DCM electrical parameters

620-0048 DCM electrical parameters include RS232 or RS422/RS485 interface, point-to-point or multidrop topology, and RS422 receiver termination (see Figure 3-2). Perform the procedure presented in Table 3-2 to set 620-0048 DCM electrical parameters.

Table 3-2 Setting 620-0048 DCM Electrical Parameters

| Step | Action                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Select physical interface. Set DCM for operation with an RS232 interface by positioning SW1 switch 3 in the CLOSED/ON state. Set DCM for operation with an RS422/RS485 interface by positioning SW1 switch 3 in the OPEN/OFF state.                                                                                                                                                                                                 |

| 2    | Select topology with SW1 switch 2. Adjust for RS422 (RS485) multidrop operation by positioning SW1 switch 2 in the CLOSED/ON state. Enabling this function allows the DCM to operate in half-duplex mode. Enable point-to-point operation by placing SW1 switch 2 in the OPEN/OFF state.                                                                                                                                            |

| 3    | If RS422 (RS485) multidrop operation is selected (SW1 switch 3 is OPEN/OFF), remove the 150-ohm resistor from RS422 RECEIVE DATA input from all DCMs except the one located at the physical end of the bus (see Figure 3-3). In that DCM, the 150-ohm resistor is enabled by positioning SW1 switch 1 in the CLOSED/ON state. In the other DCMs, the 150-ohm resistor is removed by positioning SW1 switch 1 in the OPEN/OFF state. |

Figure 3-2 DCM Serial Port with Multidrop Control

Setting 620-0048 DCM electrical parameters, continued

Figure 3-3 DCM Terminating Resistor Locations

# Setting 620-0048 DCM data link parameters

620-0048 DCM data link parameters include 620-0048 DCM nodal address, baud rate, and character format. Perform the procedure presented in Table 3-3 to set 620-0048 DCM data link parameters.

Table 3-3 Setting 620-0048 DCM Data Link Parameters

| Step | Action                                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Select network nodal addresses from 0 through 31. Position SW2 switches 4, 5, 6, 7, and 8 to corresponding states (refer to Table 3-7). Each DCM must have a unique address. Zero is used as a broadcast nodal address.                 |

| 2    | Select DCM baud rate by positioning SW3 switches 1, 2, and 3 to states corresponding to selected baud rates (refer to Table 3-8). All DCMs on the network and the host must have the same baud rate.                                    |

| 3    | Select parity with SW3 switch 4. Enable parity by positioning SW3 switch 4 to CLOSED/ON. Disable parity by positioning switch SW3 switch 4 to OPEN/OFF.                                                                                 |

| 4    | If parity is enabled (that is, SW3 switch 4 is CLOSED/ON), select the type of parity desired with SW3 switch 5. Select even parity by positioning SW3 switch 5 to OPEN/OFF. Select odd parity by positioning SW3 switch 5 to CLOSED/ON. |

| 5    | If parity is disabled (that is, SW3 switch 4 is OPEN/OFF), select the number of stop bits by positioning SW1 switch 4 to CLOSED/ON for one stop bit or OPEN/OFF for two stop bits.                                                      |

# Setting 620-0048 DCM operational parameters

620-0048 DCM operational parameters include output write protect, normal mode or flag mode operation, and 620-0048 DCM card address. Perform the procedure presented in Table 3-4 to set 620-0048 DCM operational parameters.

Table 3-4 Setting 620-0048 DCM Operational Parameters

| Step |                                                                                                                                                                                                                                    | ction                                                                   |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|

| 1    | To accept instructions that write to program memory, set SW2 switch 1 to OPEN/OFF.                                                                                                                                                 |                                                                         |  |  |

|      | To reject instructions that write to to CLOSED/OFF.                                                                                                                                                                                | program memory, set SW2 switch 1                                        |  |  |

| 2    | To accept instructions that write real outputs, or to the register tab                                                                                                                                                             | o the control output status table, to le, set SW2 switch 2 to OPEN/OFF. |  |  |

|      | To reject instructions that write to real outputs, or to the register tab CLOSED/ON.                                                                                                                                               | the control output status table, to<br>le, set SW2 switch 2 to          |  |  |

| 3    | To select normal mode operation                                                                                                                                                                                                    | , set SW2 switch 3 to CLOSED/ON.                                        |  |  |

|      | To select flag mode operation, se                                                                                                                                                                                                  | t SW2 switch 3 to OPEN/OFF.                                             |  |  |

| 4    | 4 Select DCM card address by positioning SW3 switches 7 and 8 to states corresponding to selected addresses (refer to Table 3-10). Note that only certain addresses may be assigned to DCMs located in particular CPMs as follows: |                                                                         |  |  |

|      | СРМ                                                                                                                                                                                                                                | Available Addresses                                                     |  |  |

|      | 620-10/15                                                                                                                                                                                                                          | 0                                                                       |  |  |

|      | 620-12/1633/36 † 0, 1, 2, or 3                                                                                                                                                                                                     |                                                                         |  |  |

|      | 620-20/30* 0 or 1                                                                                                                                                                                                                  |                                                                         |  |  |

|      | 620-25/35* 0, 1, 2, or 3                                                                                                                                                                                                           |                                                                         |  |  |

|      | † 620-1690/-1693 processor racks allow up to two DCMs and the 620-3691 processor rack allows up to four DCMs; each DCM must have a unique card address.                                                                            |                                                                         |  |  |

|      | * If more than one DCM is installe<br>each must have a unique card a                                                                                                                                                               | d in a 620-20/25 or 620-30/35 LCS,<br>Idress.                           |  |  |

620-0048 DCM SW1 DIP switch settings Refer to Table 3-5 for 620-0048 DCM SW1 DIP switch settings.

Table 3-5 620-0048 DCM SW1 DIP Switch Settings

| SW1<br>Switch | State      | Function                                                                                      |

|---------------|------------|-----------------------------------------------------------------------------------------------|

| 1             | CLOSED/ON* | Resistor added for point-to-point connections with RS422.                                     |

|               | OPEN/OFF   | Resistor removed for multidrop connections with RS485.                                        |

| 2             | CLOSED/ON  | Configures RS422 transmitter for multipoint operation (RS485).                                |

|               | OPEN/OFF*  | Configures RS422 transmitter for point-to-point operation, and DCM for full-duplex operation. |

| 3             | CLOSED/ON  | Selects RS232.                                                                                |

|               | OPEN/OFF   | Selects RS422/RS485.                                                                          |

| 4             | CLOSED/ON* | Selects one stop bit.                                                                         |

|               | OPEN/OFF   | Selects two stop bits.                                                                        |

<sup>\*</sup> Factory setting.

620-0048 DCM SW2 DIP switch settings Refer to Tables 3-6 and 3-7 for 620-0048 DCM SW2 DIP switch settings.

Table 3-6 620-0048 DCM SW2 DIP Switch Settings – Switches 1, 2, and 3

| SW2<br>Switch | State      | Function                                                                                                         |

|---------------|------------|------------------------------------------------------------------------------------------------------------------|

| 1             | CLOSED/ON* | DCM rejects instructions writing to program memory.                                                              |

|               | OPEN/OFF   | DCM accepts instructions writing to program memory.                                                              |

| 2             | CLOSED/ON  | DCM rejects instructions writing to the control output status table, to real outputs, or to the register table.  |

|               | OPEN/OFF*  | DCM accepts instructions writing to the control output status table, to real outpusts, or to the register table. |

| 3             | CLOSED/ON* | Selects normal mode operation.                                                                                   |

|               | OPEN/OFF   | Selects flag mode operation.                                                                                     |

<sup>\*</sup> Factory setting.

#### 620-0048 DCM SW2 DIP switch settings

Table 3-7 620-0048 DCM SW2 DIP Switch Settings – Switches 4, 5, 6, 7, and 8

| Switch 4  | Switch 5  | Switch 6  | Switch 7  | Switch 8  | ADDRESS |

|-----------|-----------|-----------|-----------|-----------|---------|

| OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | 0*      |

| CLOSED/ON | OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | 1       |

| OPEN/OFF  | CLOSED/ON | OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | 2       |

| CLOSED/ON | CLOSED/ON | OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | 3       |

| OPEN/OFF  | OPEN/OFF  | CLOSED/ON | OPEN/OFF  | OPEN/OFF  | 4       |

| CLOSED/ON | OPEN/OFF  | CLOSED/ON | OPEN/OFF  | OPEN/OFF  | 5       |

| OPEN/OFF  | CLOSED/ON | CLOSED/ON | OPEN/OFF  | OPEN/OFF  | 6       |

| CLOSED/ON | CLOSED/ON | CLOSED/ON | OPEN/OFF  | OPEN/OFF  | 7       |

| OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | CLOSED/ON | OPEN/OFF  | 8       |

| CLOSED/ON | OPEN/OFF  | OPEN/OFF  | CLOSED/ON | OPEN/OFF  | 9       |

| OPEN/OFF  | CLOSED/ON | OPEN/OFF  | CLOSED/ON | OPEN/OFF  | 10      |

| CLOSED/ON | CLOSED/ON | OPEN/OFF  | CLOSED/ON | OPEN/OFF  | 11      |

| OPEN/OFF  | OPEN/OFF  | CLOSED/ON | CLOSED/ON | OPEN/OFF  | 12      |

| CLOSED/ON | OPEN/OFF  | CLOSED/ON | CLOSED/ON | OPEN/OFF  | 13      |

| OPEN/OFF  | CLOSED/ON | CLOSED/ON | CLOSED/ON | OPEN/OFF  | 14      |

| CLOSED/ON | CLOSED/ON | CLOSED/ON | CLOSED/ON | OPEN/OFF  | 15      |

| OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | CLOSED/ON | 16      |

| CLOSED/ON | OPEN/OFF  | OPEN/OFF  | OPEN/OFF  | CLOSED/ON | 17      |

| OPEN/OFF  | CLOSED/ON | OPEN/OFF  | OPEN/OFF  | CLOSED/ON | 18      |

| CLOSED/ON | CLOSED/ON | OPEN/OFF  | OPEN/OFF  | CLOSED/ON | 19      |

| OPEN/OFF  | OPEN/OFF  | CLOSED/ON | OPEN/OFF  | CLOSED/ON | 20      |

| CLOSED/ON | OPEN/OFF  | CLOSED/ON | OPEN/OFF  | CLOSED/ON | 21      |

| OPEN/OFF  | CLOSED/ON | CLOSED/ON | OPEN/OFF  | CLOSED/ON | 22      |

| CLOSED/ON | CLOSED/ON | CLOSED/ON | OPEN/OFF  | CLOSED/ON | 23      |

<sup>\*</sup> Factory setting.

620-0048 DCM SW2 DIP switch settings, continued

Table 3-7 620-0048 DCM SW2 DIP Switch Settings – Switches 4, 5, 6, 7, and 8, Continued

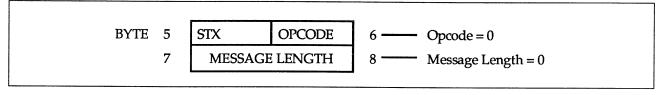

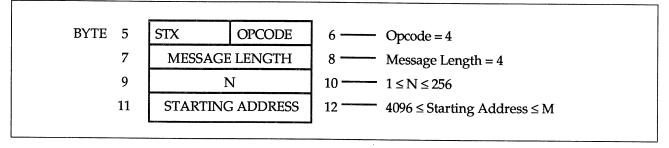

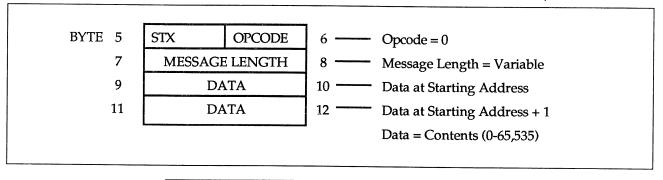

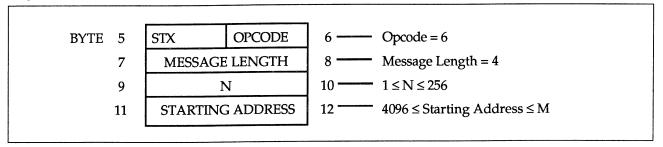

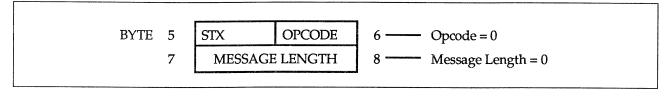

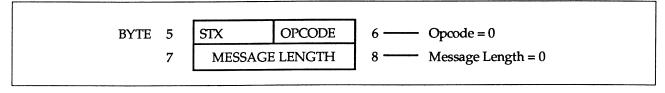

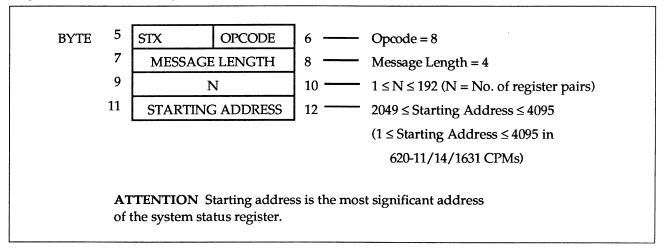

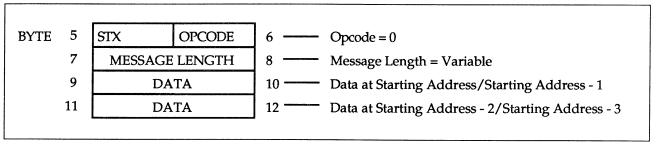

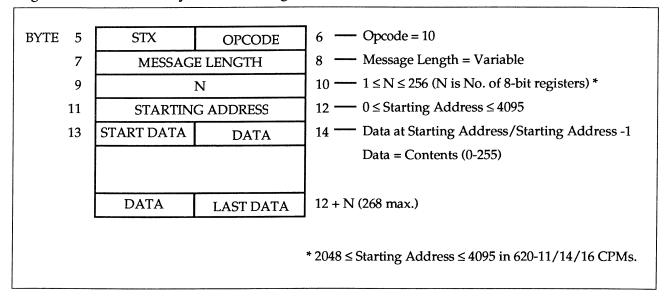

| Switch 4  | Switch 5  | Switch 6  | Switch 7  | Switch 8  | ADDRESS |